# Solutions Manual Errata for Electronics, 2nd ed. by Allan R. Hambley

#### Problem 1.17

In line two, change 3.135 W to 3.125 W.

#### Problem 1.29

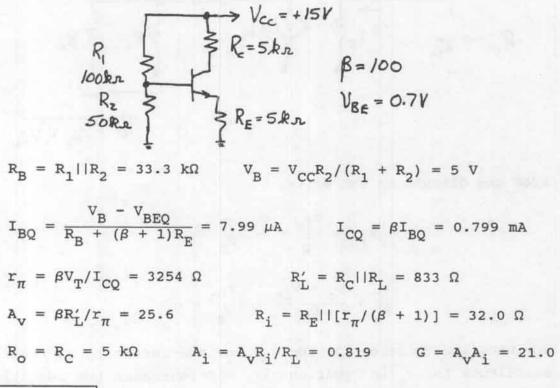

In line one, inside the first integral, delete the exponent 2 on  $i_1$ .

In line four, change

$$\frac{20/\sqrt{2}}{8}$$

to  $\frac{(20/\sqrt{2})^2}{8}$ .

In line five, change  $I_{iavg}$  to  $I_{1avg}$ .

#### Problem 1.49

Toward the end of the solution, change "when  $R_S$  changes from 1 M $\Omega$  to 10 k $\Omega$ " to "when  $R_L$  changes from 1 M $\Omega$  to 10 k $\Omega$ ".

#### Problem 1.50

Change "when  $R_S$  changes from 0 to 100  $\Omega$ " to "when  $R_L$  changes from 0 to 100  $\Omega$ ".

#### Problem 1.62

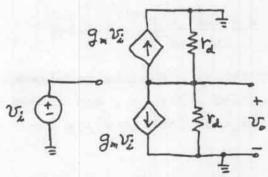

In line two of Part (b), change  $\frac{1}{2}(G_{m1}+G_{m2})R_L$  to  $(G_{m1}-G_{m2})R_L$ . Make the same change in line two of Part (c).

#### Problem 2.12

In Part (d), change

$$\frac{1}{j\omega(99C)}$$

to  $\frac{1}{j\omega(101C)}$ .

In the last paragraph, change 99-pF to 101-pF.

#### Problem 2.14

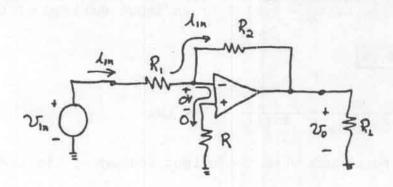

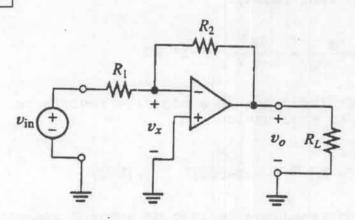

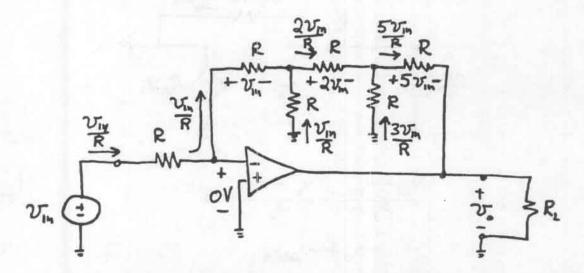

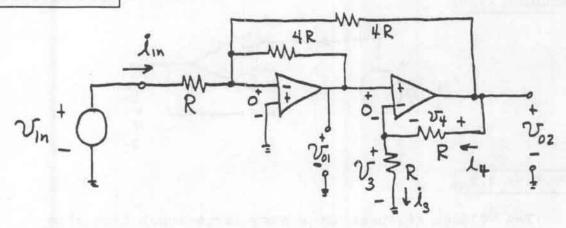

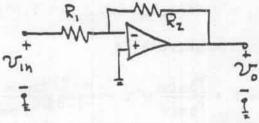

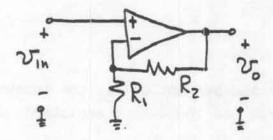

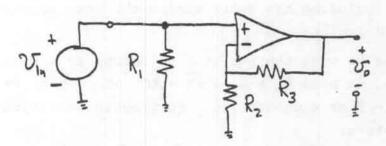

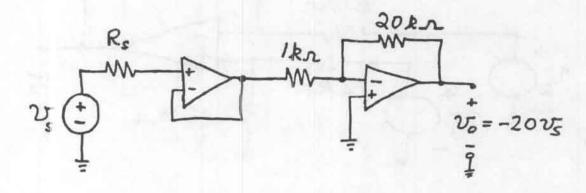

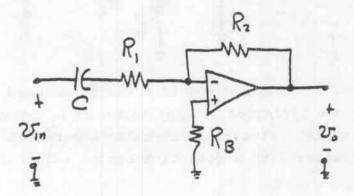

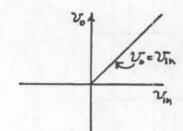

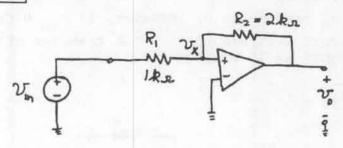

After the figure, change  $v_0 = 8v_{in}$  to  $v_0 = -8v_{in}$  and change the gain from 8 to -8.

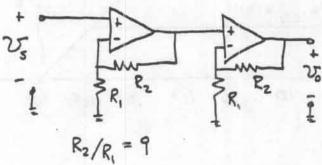

#### Problem 2.16

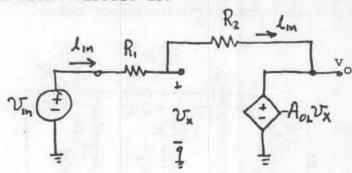

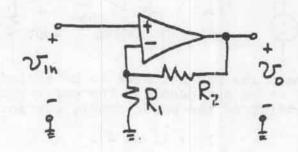

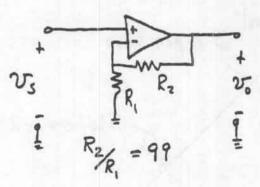

At the end of the solution, after "For  $AOL = 10^5$ ", change  $A_V = -9.998$  to  $A_V = -9.9989$  and change  $-R_2/R_1 = 10$  to  $-R_2/R_1 = -10$ .

#### Problem 2.33

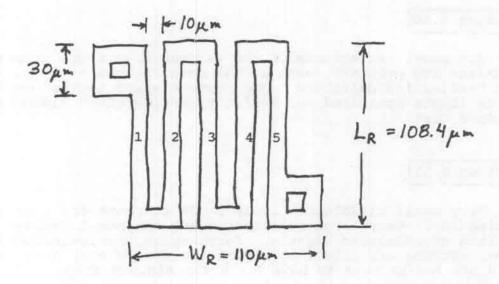

The problem statement should have specified  $W_{space}$  = 10  $\mu$ m instead of 5  $\mu$ m.

#### Problem 2.38

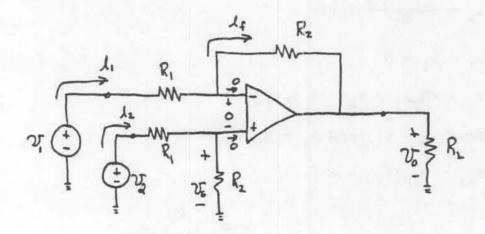

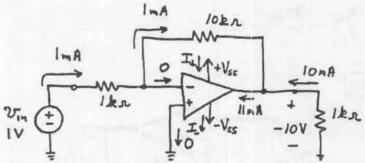

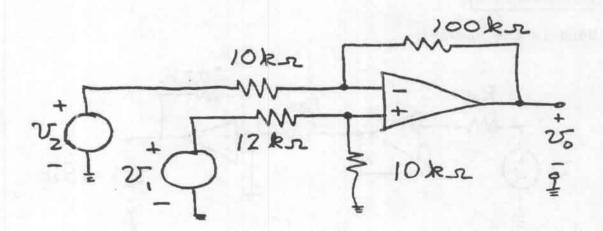

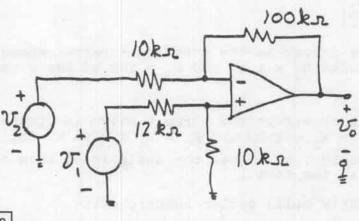

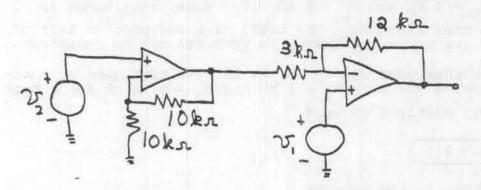

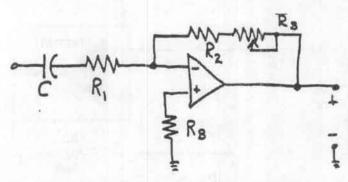

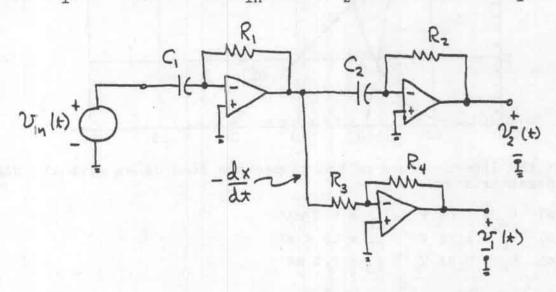

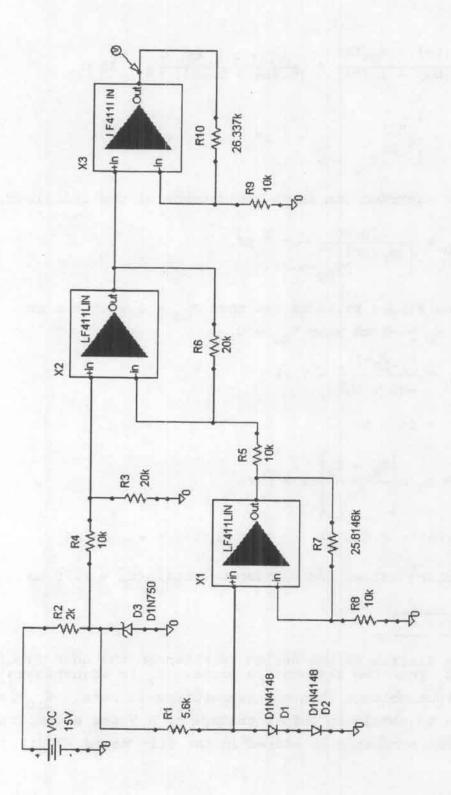

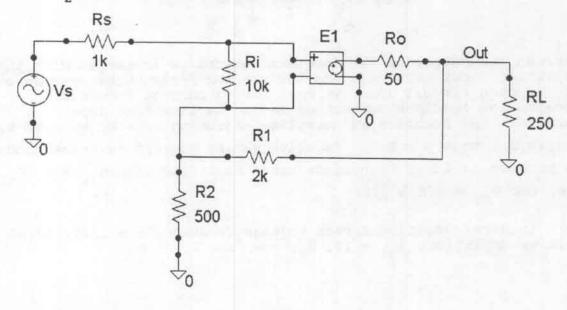

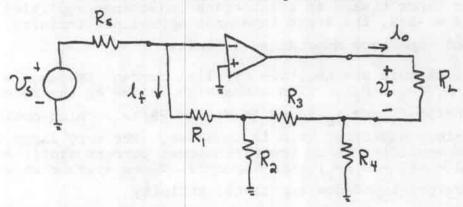

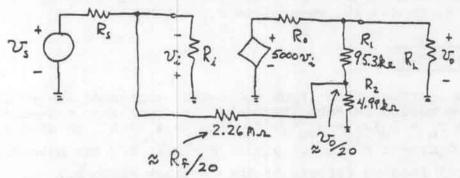

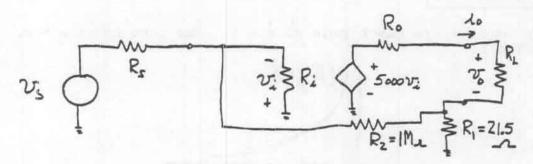

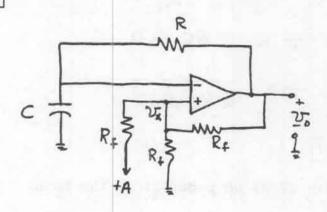

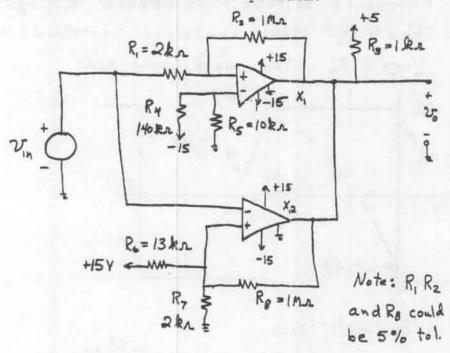

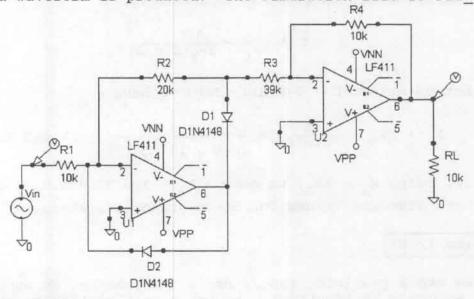

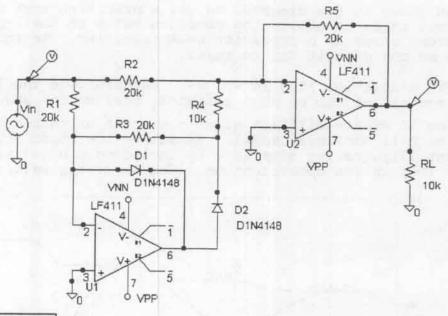

In the figure, change the upper 10-k $\Omega$  resistor (connecting the inverting input to the output of the first op amp) to 15 k $\Omega$ .

#### Problem 2.43

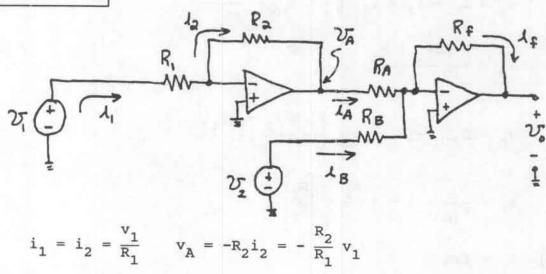

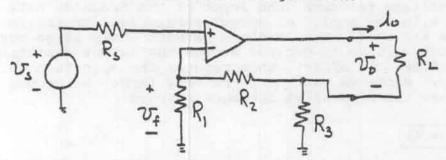

In Part (b), Equation (4), change  $R_1$  to  $R_2$ . In Part (c), in the first equation after the figure, change  $v_i$  to  $-v_i$ .

#### Problem 2.53

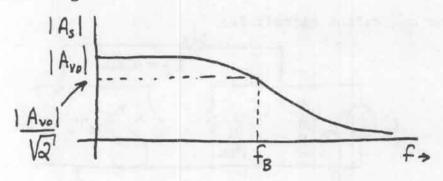

In the first line, change focl to fBCL.

#### Problem 2.73

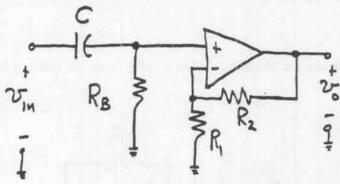

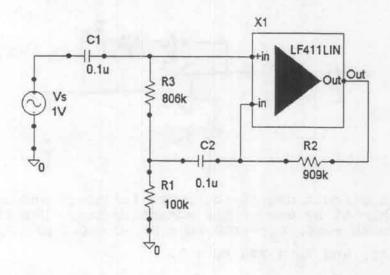

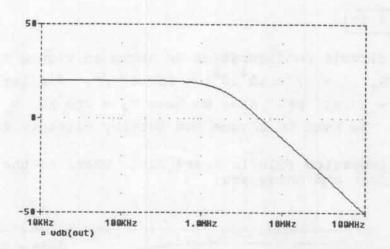

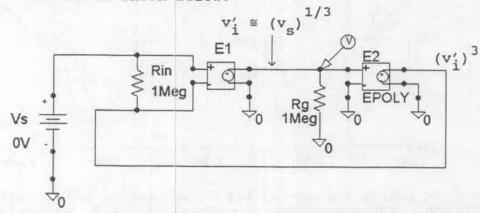

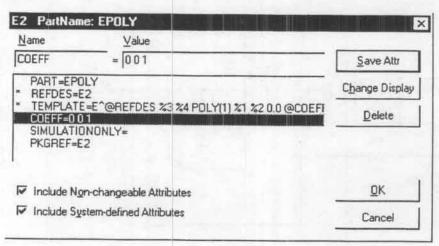

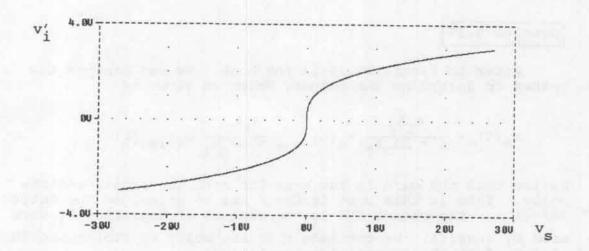

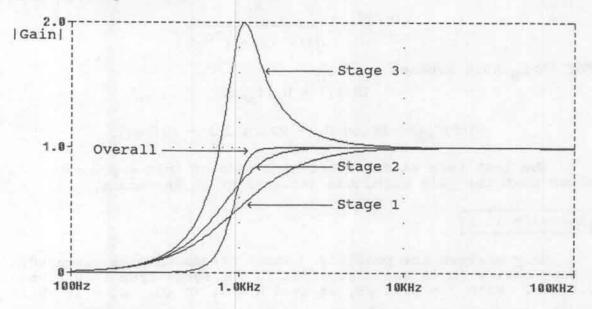

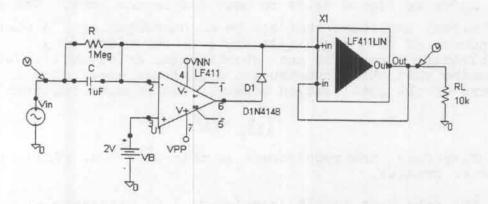

Before the figure, add the sentence: "The PSpice simulation is stored in the file named  $P2\_73$ ."

#### Problem 2.75

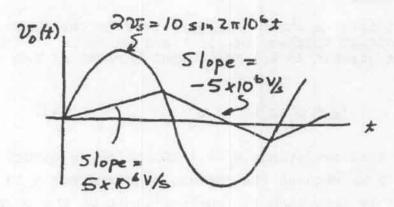

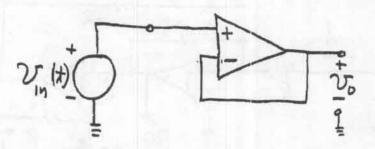

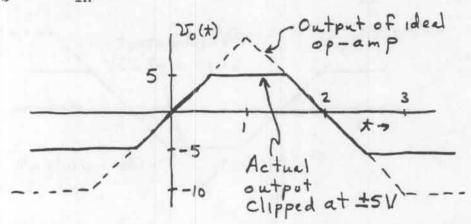

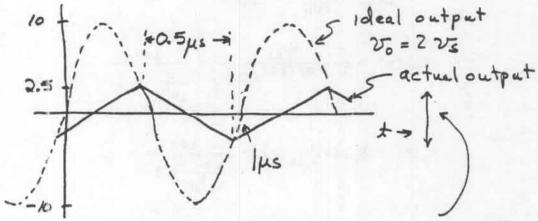

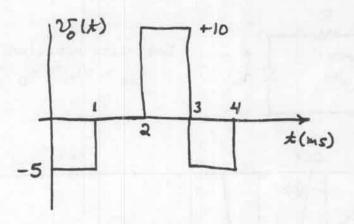

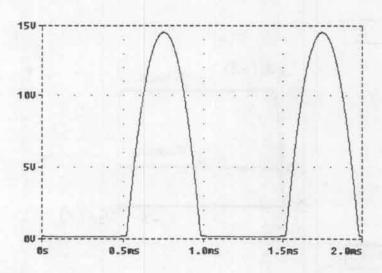

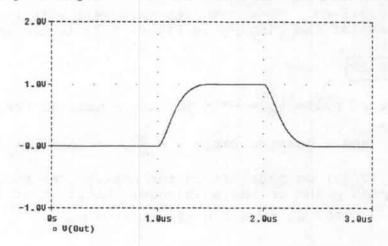

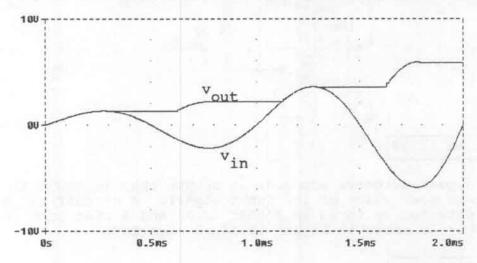

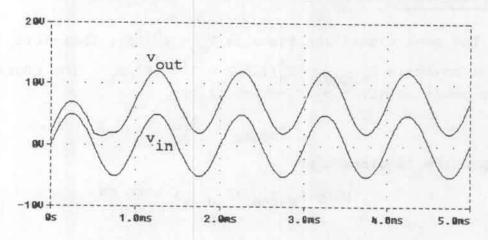

Delete the sentence stating that the plot of  $v_0(t)$  is on the next page.

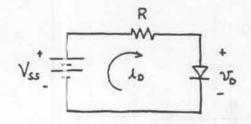

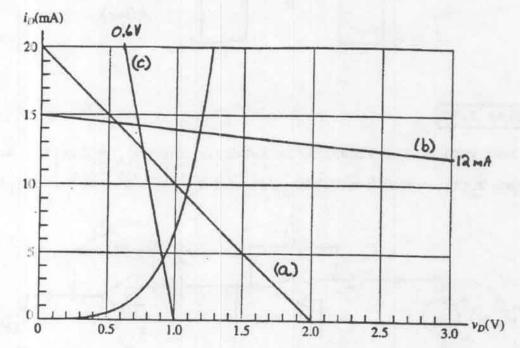

#### Problem 3.10

In line three (an equation), change  $i_D/R$  to  $v_D/R$ .

#### Problem 3.53

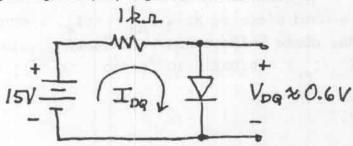

In the sentence beginning with "The dynamic resistance", change  $nV_T/I_{CQ}$  to  $nV_T/I_{DQ}$ .

#### Problem 3.56

In Part (a), change  $nV_T/I_{CQ}$  to  $nV_T/I_{DQ}$ .

#### Problem 3.57

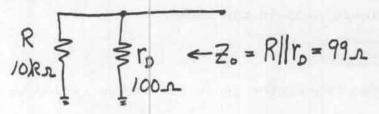

The solution uses  $r_d$  for the diode resistance rather than  $r_z$  as specified in the problem statement.

#### Problem 3.58

In Part (c), line two (an equation), change the minus sign inside the parentheses to a plus sign.

#### Problem 3.70

In line one, change "electon" to "atom".

#### Problem 3.90

In Part (c), line one, change the denominator of the fraction in parentheses from  $I_R$  to  $-I_R$ .

#### Problem 3.92

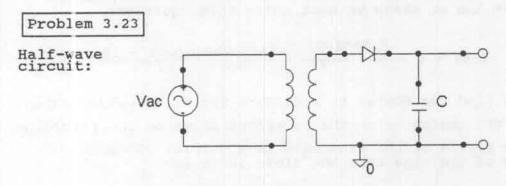

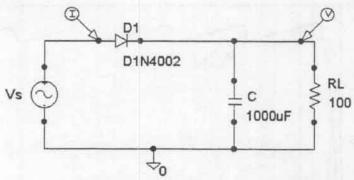

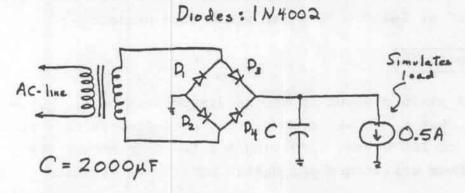

At the end of the solution, add: "Larger capacitance produces less output voltage ripple and higher peak diode current".

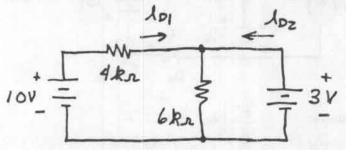

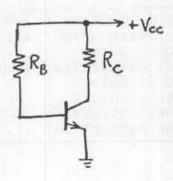

#### Problem 4.10

In line five of the solution (an equation), change "10 - 0.6585" to "0.6585 - 10".

#### Problem 4.25

In the equation for  $I_S$  (line seven of the solution), each of the two denominators should end with ) -1 instead of -1).

#### Problem 4.34

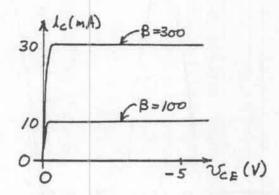

In the line for part (d) with  $\beta$  = 100, we should have I = 9.53 mA (instead of 10 mA) and V = 9.53 V (rather than 10 V).

#### Problem 4.45

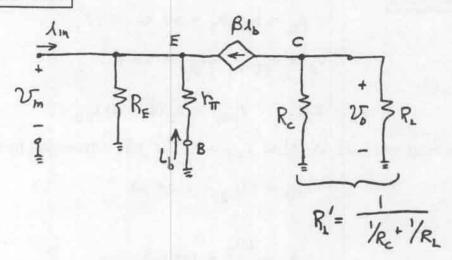

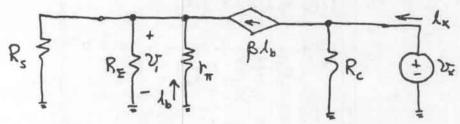

Change

$$A_{VO} = -\beta R_L/r_{\pi}$$

to  $A_{VO} = -\beta R_C/r_{\pi}$ .

#### Problem 4.50

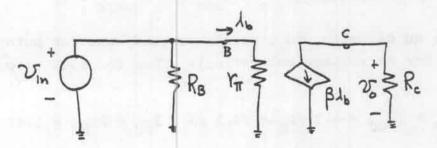

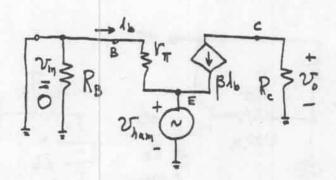

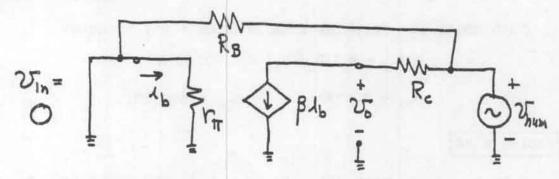

At the end of step one, add: "Set all other independent signal sources to zero."

#### Problem 4.54

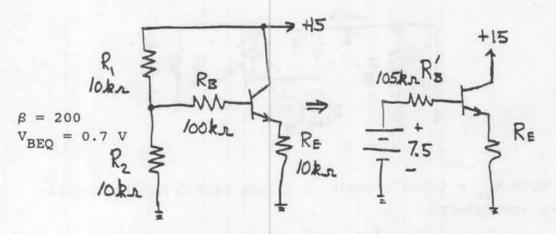

Next to the figure, change  $V_{EQ}$  to  $V_{BEQ}$ .

#### Problem 4.60

In the first line after the figure, second equation, change  $I_{\textit{BEQ}}$  to  $I_{\textit{BQ}}$ .

#### Problem 4.65

In the first line after the figure, insert an equals sign after  $I_B$ .

#### Problem 5.3

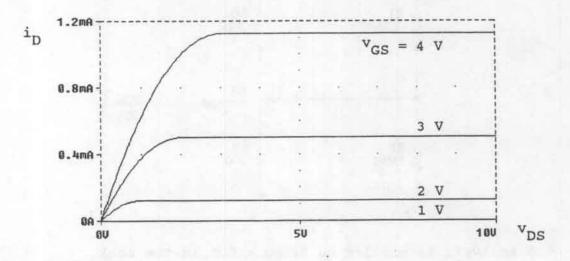

Calculation of the drain currents was omitted. The drain currents are:

(a)

$$i_D = K(v_{GS} - V_{to})^2 = (W/L)(KP/2)(v_{GS} - V_{to})^2 = 2.25 \text{ mA}$$

(b)

$$i_D = K[2(v_{GS} - V_{to})v_{DS} - (v_{DS})^2]$$

=  $(W/L)(KP/2)[2(v_{GS} - V_{to})v_{DS} - (v_{DS})^2]$

=  $2 \text{ mA}$

(c)  $i_D = 0$

#### Problem 5.7

In the last sentence, change K = 25 to  $K = 25 \mu A/V^2$ .

#### Problems 5.23

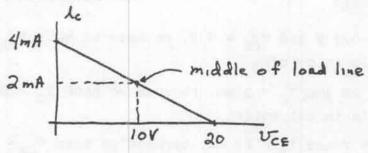

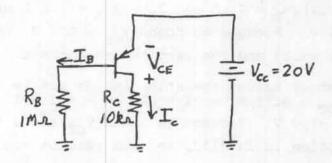

The last line of part (a) should read:  $V_{DSO}$  = 20 - 2 $I_{DO}$  = 12 V.

#### Problem 5.25

Change the second equation from  $R_SI_{DSQ}$  = 6 V to  $R_SI_{DQ}\cong$  6 V.

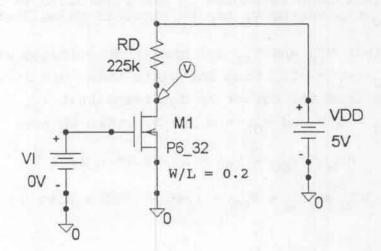

#### Problem 5.46

Change "greater than zero" to "greater than unity".

#### Problem 5.65

In the third-to-last sentence, change  $K(v_{GS5} - V_{to})$  to  $K(v_{GS5} - V_{to})^2$ .

#### Problem 5.74

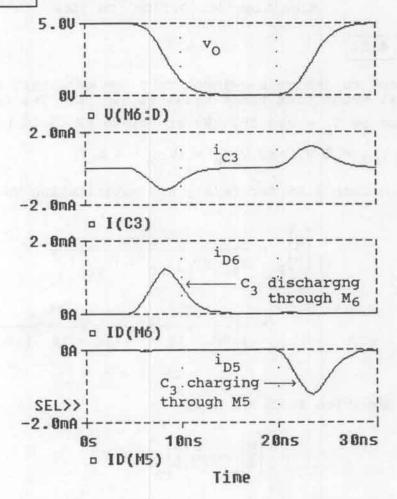

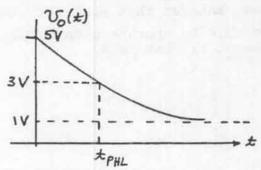

In the sentence after the opening equation, change "saturation" to "triode region". In part (c) before the table, insert "Using the value of C given in part (d) of the problem, we have:"

#### Problem 6.16

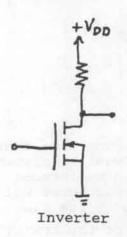

At the beginning of the solution, insert "The following solution is for an inverter operating at 400 MHz." At the end of the solution, add "For an inverter operating at 400 Hz,  $P_{dynamic}$  = 3.6 x 10<sup>-10</sup> W."

#### Problem 6.23

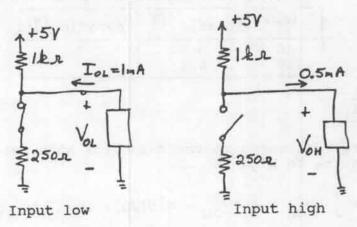

In the third line, change " $I_{OL}$  = -1 mA" to " $I_{OL}$  = 1 mA".

#### Problems 6.24

In the first line, change " $P_{dynamic}$  = If" to " $P_{dynamic}$  = Kf".

#### Problem 6.25

In the equation for Energy, change  $(4^2 - 1^2)$  to  $(5^2 - 0^2)$  and change 150 pJ to 250 pJ. In the equation for  $P_{dynamic}$ , change 150 to 250 and change 3.75 mW to 6.25 mW.

#### Problem 6.32

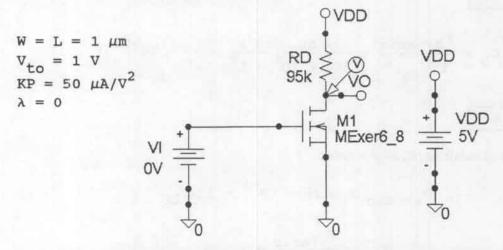

In the circuit diagram, the device should be an enhancement MOSFET rather than a depletion MOSFET.

#### Problem 6.36

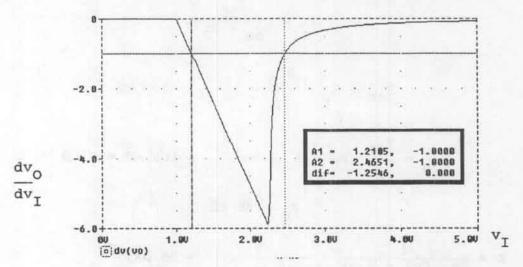

Change the middle of the fourth line to read " $V_{IH}$  = 2.04 V,  $V_{IL}$  = 1.08 V".

#### Problem 6.51

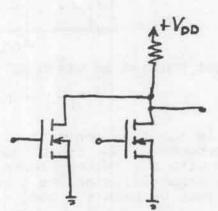

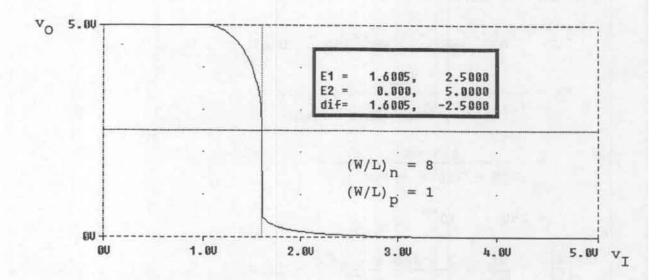

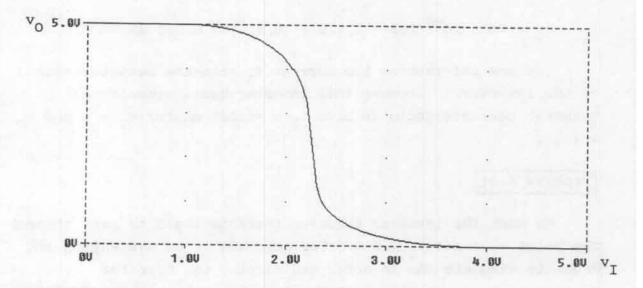

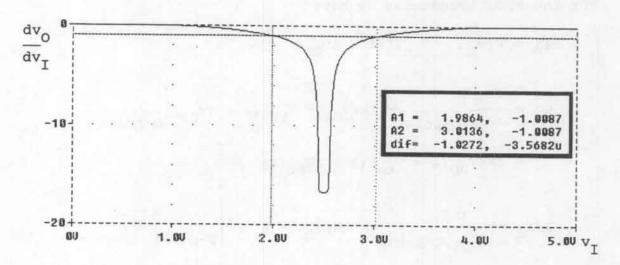

At the end of the first paragraph, just before the figure, insert the following: [Note: The solution assumes  $(W/L)_p = 1$ . On the other hand for  $(W/L)_p = 2$ , we would need  $(W/L)_n = 16$ .]

#### Problem 7.1

Delete the comma after the phrase "high precision".

#### Problem 7.11

In the first sentence, change "below" to "on the next page".

#### Problem 7.18

Toward the end of the main paragraph, in the equation for  $R_2$ ,

insert a left-hand parenthesis the before 26mV.

#### Problem 7.20

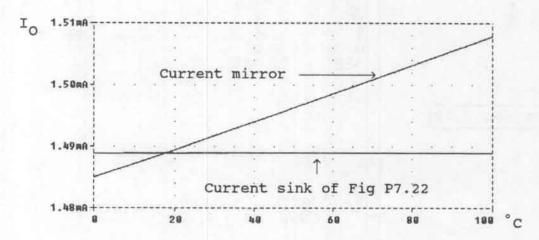

Actually the current decreases when  $\beta$  decreases. Thus, the percentage increase should be stated as -0.99%.

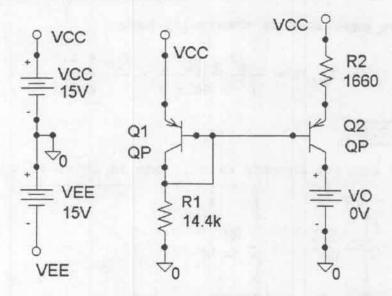

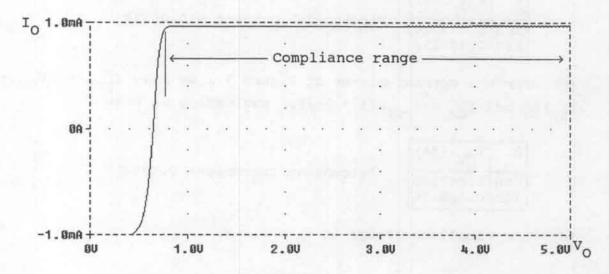

#### Problem 7.22

At the beginning of part (a), add the following: (Note: The problem should have asked for proof that  $I_O$ , rather than  $I_{C2}$ , is independent of  $V_{BE}$ .)

#### Problem 7.25

In the first line, change  $V_{CC}$  in the fraction numerator to 10.

#### Problem 7.28

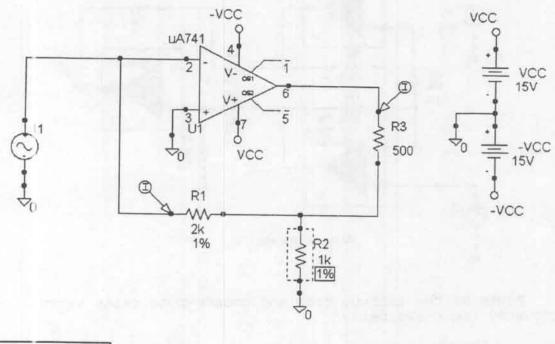

In the first sentence after the diagram, change P7\_27 to P7\_28.

#### Problem 7.37

In the third line, change (15 +  $V_{GS1}$  -  $V_{GS3}$ ) to (15 -  $V_{GS1}$  -  $V_{GS3}$ ).

#### Problem 7.38

At the beginning of the solution, add the following: "The problem statement should refer to Figure P7.38, not P7.36."

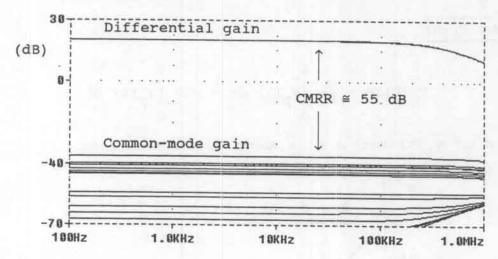

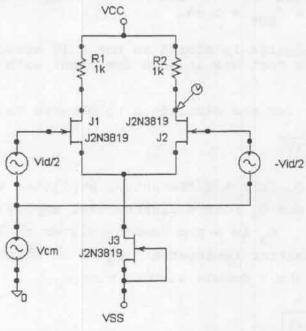

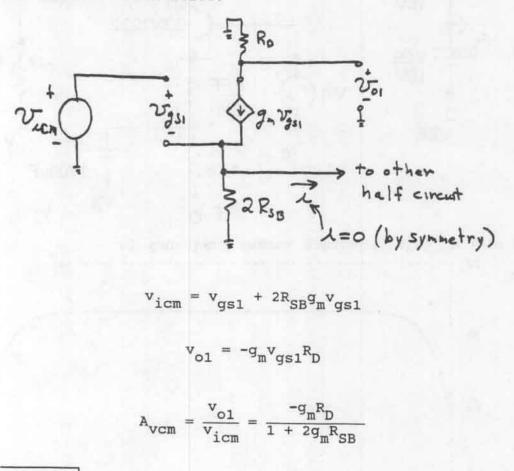

#### Problems 7.60 and 7.61

In the next-to-last sentence of each solution, change  $A_{cm}$  to  $A_{vcm}$ .

#### Problem 7.65

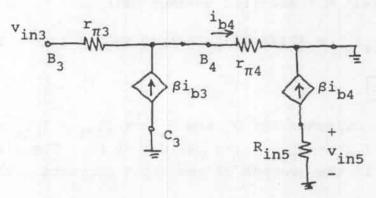

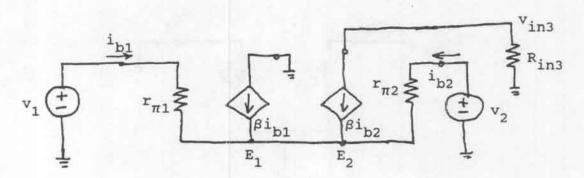

In the first paragraph, change the value found for  $A_{v1}$  from 64.6 to 36.23. At the end of the solution, change the value found for the overall gain  $A_v$  from  $20.4 \times 10^3$  to  $11.5 \times 10^3$ .

#### Problem 7.66

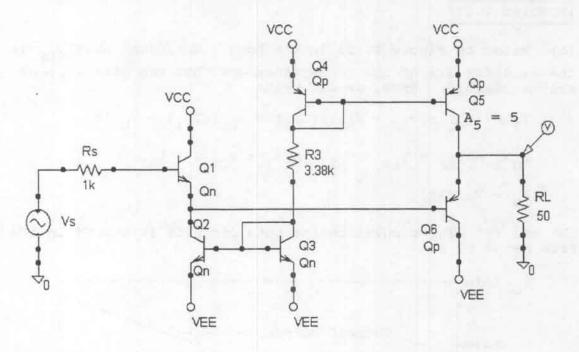

At the end of the solution, add the following sentence: "The pnp stage drops the dc level down so it comes out zero after the last  $(Q_6)$  stage."

#### Problem 7.67

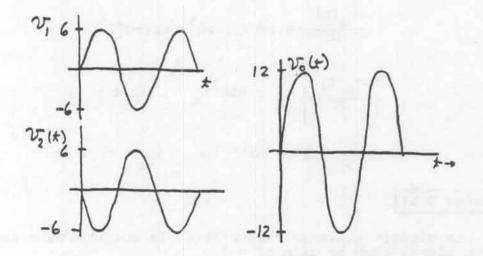

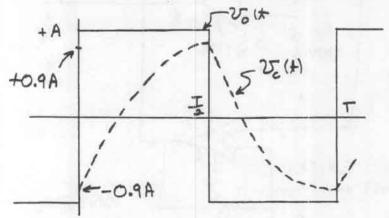

Throughout the solution, change all occurrences of  $2000\pi t$  to  $200\pi t$ .

#### Problem 7.71

After the diagram, add the following: (Note: For the transistors to operate in the active region, the emitters of the current sinks must be connected to  $-V_{EE}$  rather than to ground.)

In the third line of the main paragaph, change " $Q_3$  is a simple mirror" to " $Q_8$  is a simple mirror".

#### Problem 7.74

In the the top line of page 327, change  $(10 \mu A)/\beta$  to  $(100 \mu A)/\beta$ .

#### Problem 7.75

At the very end, change the value found for  $A_1/A_2$  from 0.953 to 0.926.

#### Problem 8.8

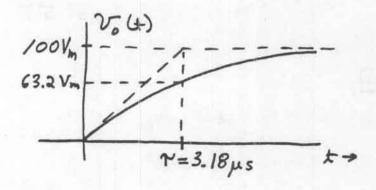

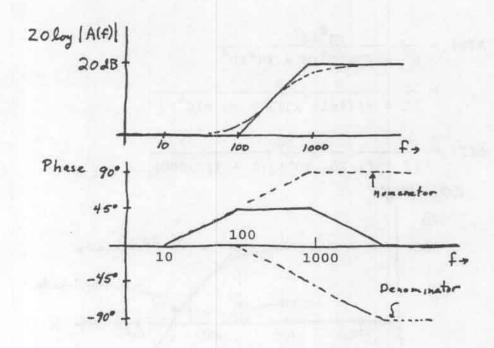

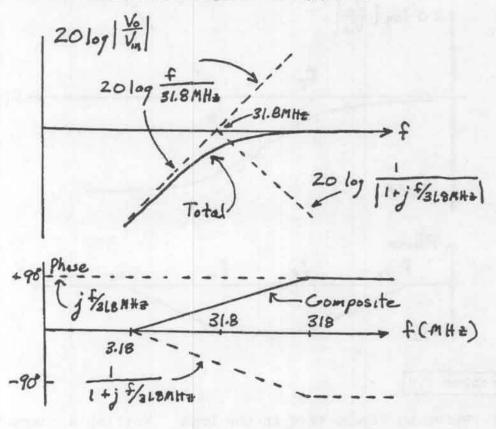

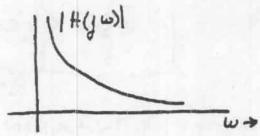

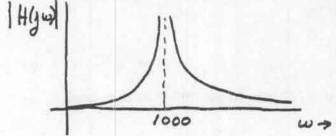

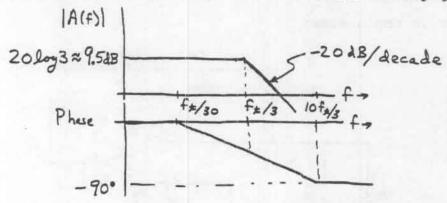

In part (a) of the solution, the components of the phase plot are incorrectly added. The correct phase plot should show a phase of  $+90^{\circ}$  for low f,  $0^{\circ}$  for high f, and should decrease in a straight line between 3.18 MHz and 318 MHz.

#### Problem 8.14

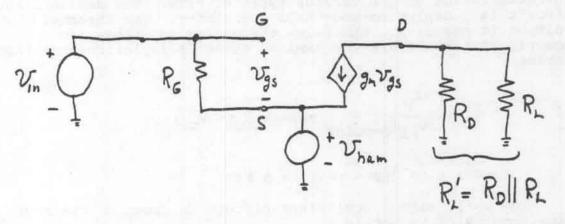

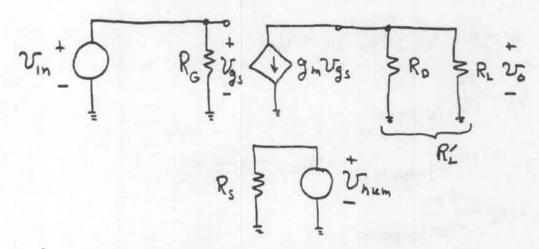

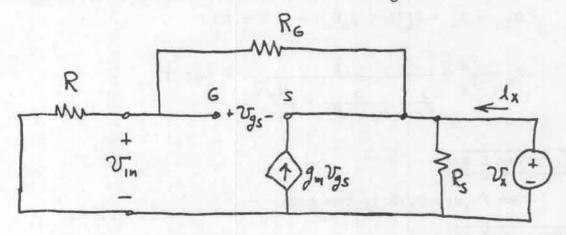

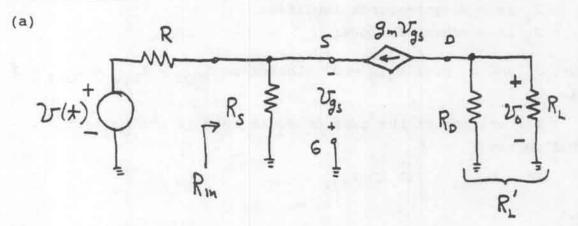

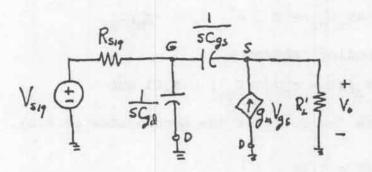

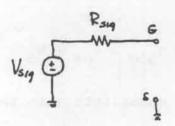

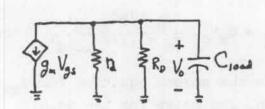

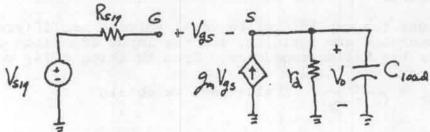

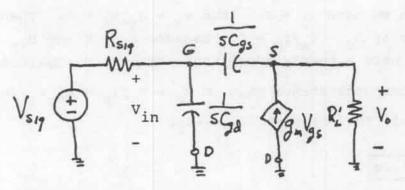

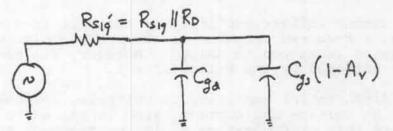

In the first line of part (b), change "drain" to "source". Notice that the expression abbreviated as B simplifies to  $C_{gs}(R_{sig} + R'_{L}) + C_{gd}R_{sig}(g_{m}R'_{L} + 1)$ , and the expression abbreviated as A simplifies to  $C_{gs}C_{gd}R_{sig}R'_{L}$ .

#### Problem 8.18

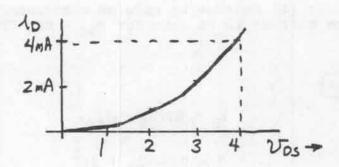

In part (e), change " $r_d$  =  $\infty$  (because  $\lambda$  = 0)" to " $r_d$   $\cong$   $1/\lambda I_{DQ}$  = 40 k $\Omega$ ". Change the sentence about the break frequency to read simply: "The break frequency is 251 kHz."

Problem 8.24

Change the table to appear thus:

| $R_L$                                 | 1 kΩ            | 10 kΩ           |

|---------------------------------------|-----------------|-----------------|

| $R_{\!\scriptscriptstyle L}^{\prime}$ | 995 Ω           | 9.52 k $\Omega$ |

| $A_V$                                 | -4.99           | -9.05           |

| R <sub>in,Miller</sub>                | 33.4 k $\Omega$ | 19.9 k $\Omega$ |

| $R_{\times}$                          | 25.0 k $\Omega$ | 16.6 k $\Omega$ |

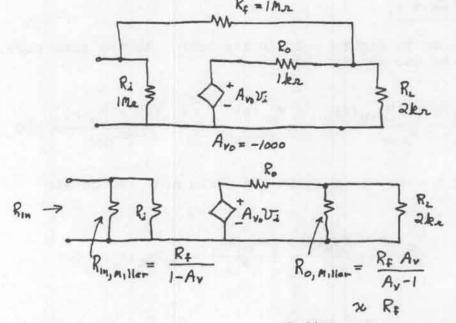

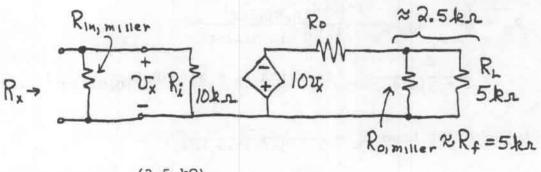

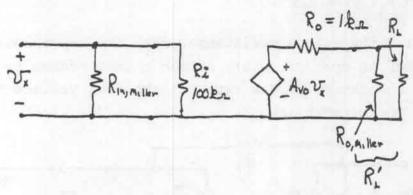

#### Problem 8.25

Change the second line after the first figure to read:

$$Rin = Ri | |Rin Miller| \approx 0.1 \Omega.$$

#### Problem 8.30

Change "Equations 8.41 and 8.42" to "Equations 8.42 and 8.43".

#### Problem 8.33

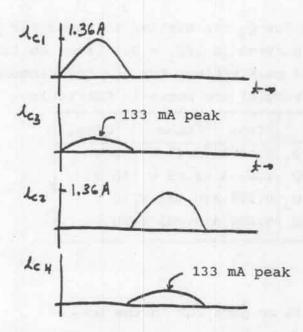

In the second line change "Problem 8.33" to "Problem 8.32". In the equation for  $i_C$ , change  $50 sin(2000\pi t)$  to  $500 sin(2000\pi t)$ . Change the value found for  $I_{C,rms}$  to  $354~\mu A$ .

#### Problem 8.36

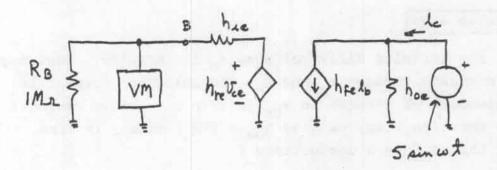

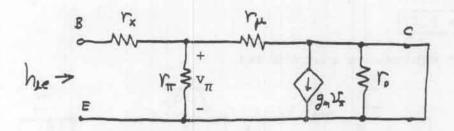

Note that in the equation for  $h_{0e}$ , the current term  $\frac{1}{r_{\pi}+r_{\mu}}$  is small, and has been ignored.

#### Problem 8.40

In the first line of part (a), in the equation for  $I_{BQ}$ , change "100" to "(1mA)/100".

#### Problem 8.42

In the table, change the units of the right-column value of  $R_E$  from m $\Omega$  to M $\Omega$ .

#### Problem 8.43

In the middle of part (a), "Solving Equation (2) for  $v_o$ " should read "Solving Equation (2) for  $v_{\pi}$ ". In part (b),  $R_{EF}$  should be  $R_{E1}$ .

#### Problem 8.56

In the second circuit diagram, change  $R'_{sig} = R_{sig} || R_D$  to  $R'_{sig} = R_{sig} || R_G$ .

#### Problem 8.66

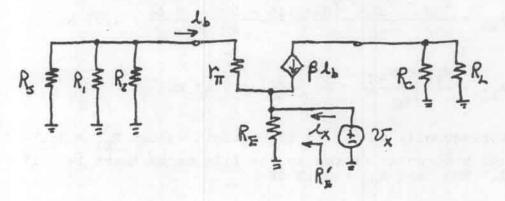

The derivation of  $C_1$  should read as follows:

Thus, the input resistance of the amplifier is

$$R_{in} = R_B ||[r_{\pi 1} + (\beta + 1)(R_{E1}||R_{E2}||r_{e2})]| = 1046 \Omega$$

The resistance in series with  $C_1$  is  $R_{in} + R_s = 1096 \Omega$ .

$$C_1 = 1/(2\pi f_1 1096) = 1/(2\pi 10 \times 1096) = 14.5 \,\mu\text{F}$$

Also, in the equation for  $C_2$ , change " $1/(2\pi f_2 1168)$ " to " $1/(2\pi f_2 1020)$ ".

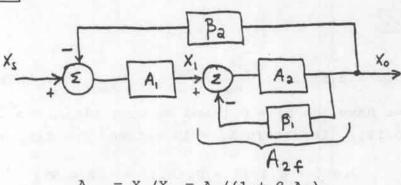

#### Problem 9.7

In part (a) of the solution, the final equation should read

$$A_{f} = \frac{X_{o}}{X_{s}} = \frac{A_{1}A_{2f}}{1 + \beta_{2}A_{1}A_{2f}} = \frac{A_{1}A_{2}}{1 + \beta_{1}A_{2} + \beta_{2}A_{1}A_{2}}$$

Also, in line four of part (b) change  $A_2$  to  $A_3$  and change "a a gain" to "a gain".

#### Problem 9.10

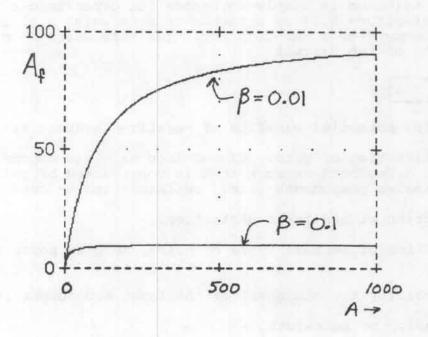

Change > to >>.

#### Problem 9.14

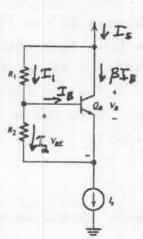

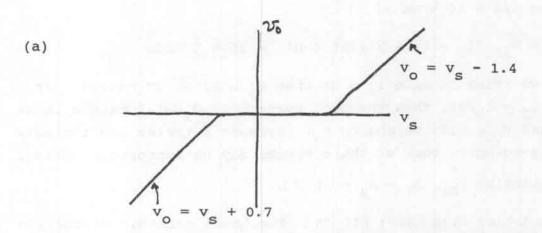

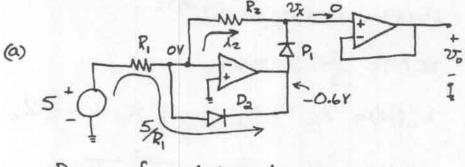

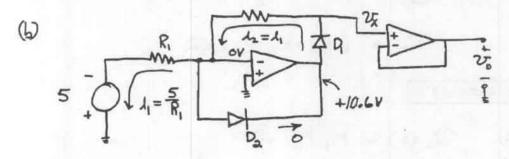

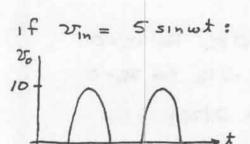

Part (a) uses  $|V_{BE}| = 0.7$  V in saturation, not 0.6 V as specified in the problem.

#### Problem 9.35

In the first line, delete the second occurrence of  $i_i$ .

#### Problem 9.44

In the last line, change "parallel" to "voltage".

#### Problem 9.45

The last sentence, should read: "Since we want Aß to be very large in magnitude, we choose small resistances for a current feedback network."

#### Problem 9.47

At the very end of the solution, change the units of the value found for  $R_{\it of}$  from  $\Omega$  to  $k\Omega$ .

#### Problem 9.49

The problem should have called for  $R_{mf}$  = -5000  $\Omega$ . In the solution, change the units of the value found for  $R_{if}$  from  $M\Omega$  to  $\Omega$ .

#### Problem 9.51

In the third line of part (a), delete the second occurrence of  $v_i$ .

#### Problem 9.52

In part (a) change the equation that begins line four to

$$v_o/i_i = -A_i R_i \times \frac{R_L}{R_o + R_L} = -417 \text{ M}\Omega$$

In the last line of part (a), add a negative sign in front of the value found for  $\beta$ . In the fourth line of part (b), change  $\beta = 1/R_f$  to  $\beta = -1/R_f$ .

#### Problem 9.53

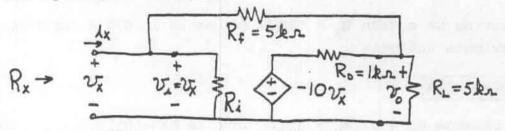

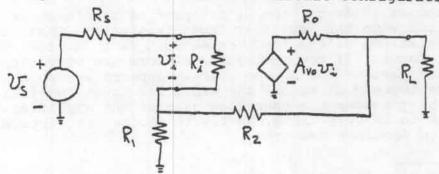

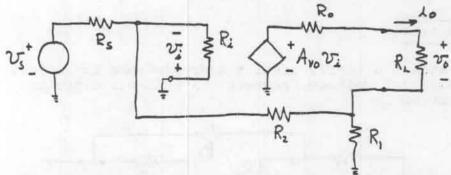

In the third line of part (a), add a negative sign in front of  $A_{VO}R_i$ . At the end of part (a), change the value found for  $\beta$  to  $-2.16\times 10^{-5}$ . In part (b), in the first line after the diagram, add a negative sign after the = and before the fraction.

#### Problem 9.59

In part (d), change both instances of "1000t'' to "100t''.

#### Problem 9.64

In the last line, change 3500 Hz to 350 Hz.

#### Problem 9.66

In the next-to-last line, change "imaginary" to "complex".

#### Problem 9.72

In the next-to-last line, change  $180^{\circ}$  to  $-180^{\circ}$ .

#### Problem 9.86

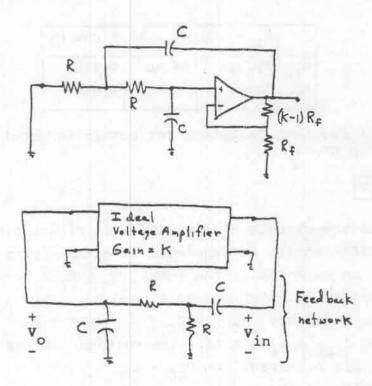

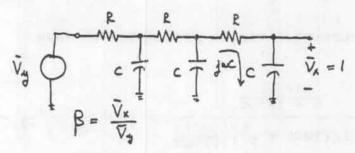

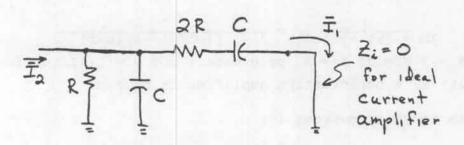

In part (c), the last two sentences should read: "Finally setting Aß = 1 yields A = -29 and  $\omega = \sqrt{6} / (RC)$ . Thus an inverting amplifier is needed."

In part (d), change the sign on the last term from - to + in the denominator of the second equation.

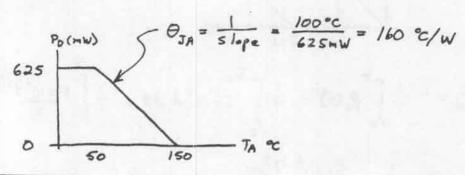

Delete the closing parenthesis after 0.0025 in the middle of the first equation. Change the value found for  $\theta_{JA}$  to 150 °C/W.

Problem 10.23

The trigonometric identity should read  $2\sin^2(x) = 1 - \cos(2x)$ . In the integral equation that follows, change  $10\sin(4000\pi t)$  to  $10\cos(4000\pi t)$ .

Problem 10.27

In the fifth line, change the integrand to  $[1 - \cos(2\omega t)]$ .

Problem 10.35

In part (a), change  $(V_{cc}/\sqrt{2})R_i$  to  $(V_{cc}/\sqrt{2})^2/R_i$ .

Problem 10.37

In part (d), the final equation should read  $P_{Q1\text{max}} = (V_{CC}/2) \times V_{CC}/(2R_L) = V_{CC}^2/(4R_L) = 7.03 \text{ W}.$

Problem 10.45

In Equation 10.49 in the text,  $\frac{R_2}{R_1 + R_2}$  should be replaced by  $\frac{R_1 + R_2}{R_2}$ .

Problem 10.50

In the second line of the solution, change "op amp" to "transistor".

**Problem 10.63**

In the second line, change "on the next page" to "below".

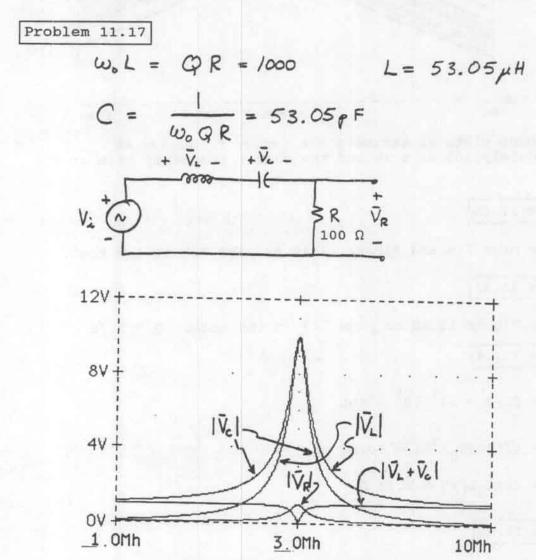

Problem 11.16

In the equation for C, insert a closing square bracket after the L.

Problem 11.21

In the third line of the solution, change  $\omega_R = 3\omega_0$  to  $f_R = 3f_0$ .

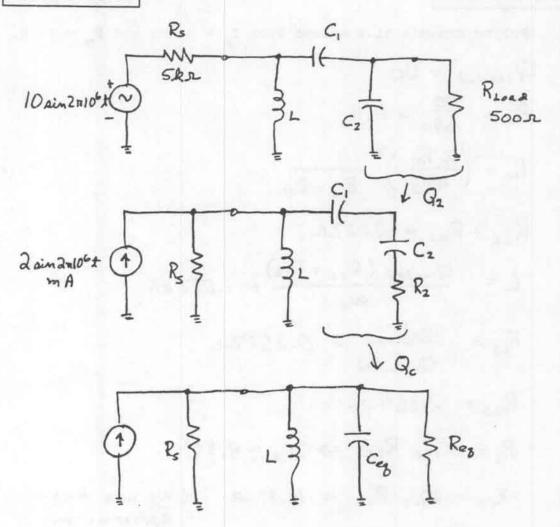

In the first line after the last set of diagrams, change  $Q_2^2=R_L/R_s$  to  $Q_2=\sqrt{R_L/R_s}$  .

Also note that in the first diagram of the solution,  $R_S$  represents the internal source resistance, while in the rest of the solution,  $R_S$  represents the series equivalent of  $R_I$ .

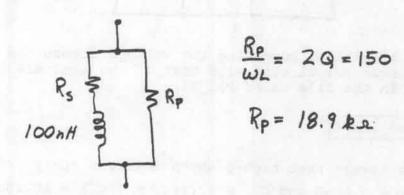

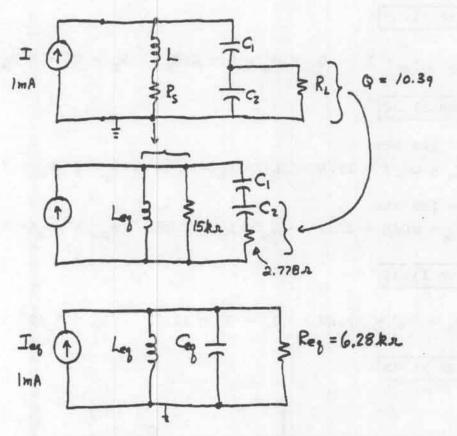

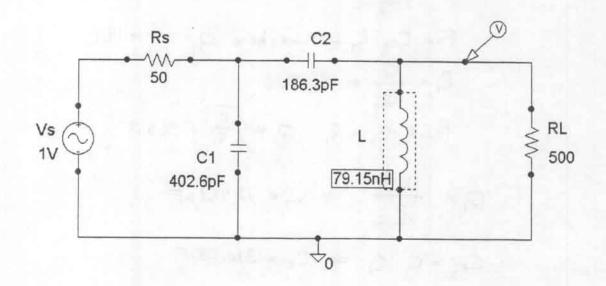

#### Problem 11.38

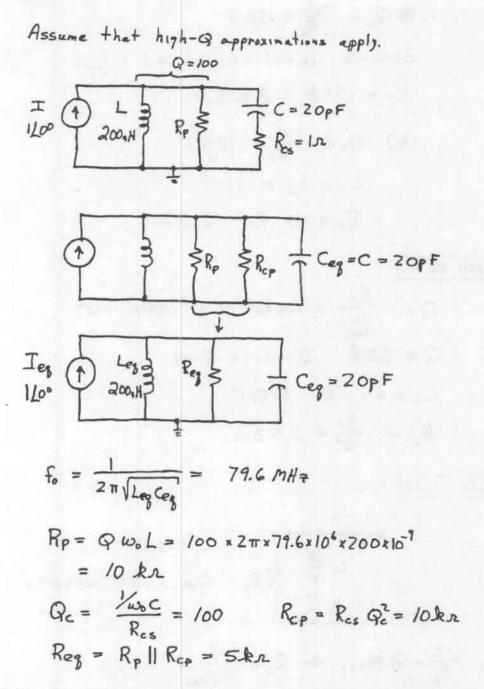

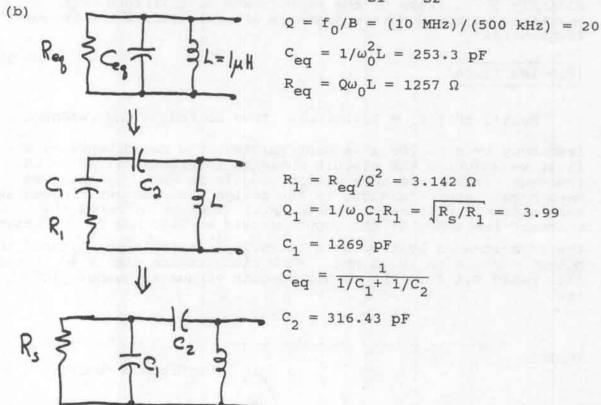

Note that  $R_s$  represents the series equivalent of  $R_L$ . In the second line, note that  $Q_C$  = 10 and change the value found for  $R_S$  to 5  $\Omega$ . In the third line, change 4.47 to 3.16, change 1423.5 to 1006.6, and change 409.77 to 465.2. Then the simulation results closely match predictions.

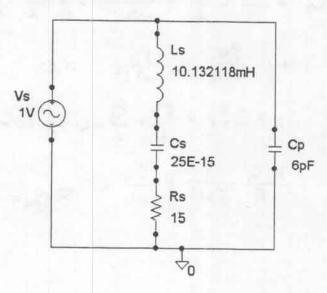

#### **Problem 11.39**

Note that  $R_s$  represents the series equivalent of  $R_L$ . In the second line, change the value found for  $R_s$  to 50 m $\Omega$ . (Note that  $Q_c$  = 100.)

#### **Problem 11.45**

In part (c), change 256.51 pF to 316.43 pF and change 20.21 nF to 1269 pF.

#### Problem 11.50

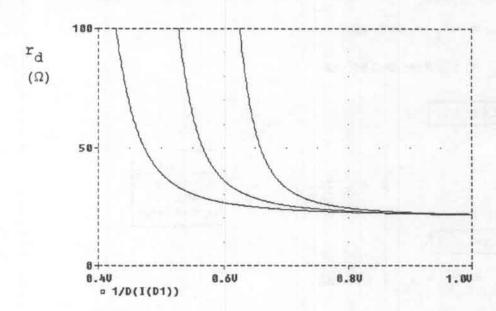

Note that in the solution  $r_d$  has been taken to be very large.

#### Problem 11.54

At the end of the solution sentence, change the period to a comma and add "or approximately 20 MHz. The third overtone frequency is about 30 MHz."

#### **Problem 11.57**

Note that "antiresonant frequency" means the same thing as "parallel-resonant frequency."

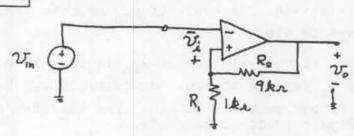

#### Problem 12.11

Note that in the solution, "node 2" refers to the noninverting input.

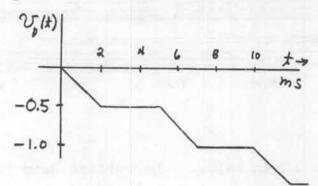

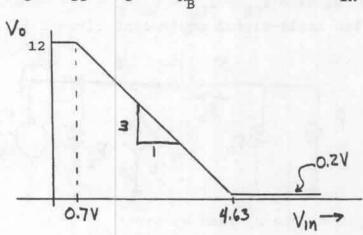

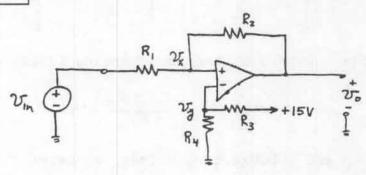

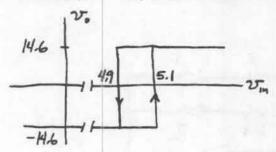

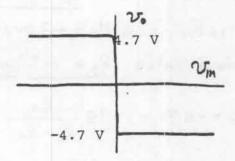

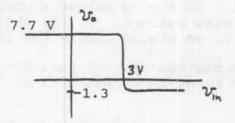

After the first paragraph, change  $v_0 = VB + 4.7$  to  $v_0 = VB - 4.7$ . After the second paragraph, change  $v_0 = VB - 4.7$  to  $v_0 = VB + 4.7$  and change  $v_{in} > VB$  to  $v_{in} < VB$ . In the plot at the end of the solution, change -1.3 on the y-axis to -1.7.

#### **Problem 12.17**

Note that in the problem statement, the  $\textit{v}_2$  referenced in the ninth line should be  $\textit{v}_1$  .

#### Problem 12.40

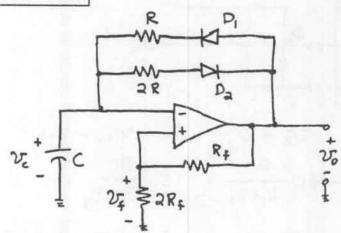

At the end of the solution, change  $i_0R/2$  to  $-i_0R/2$  and change 9.96 V to - 9.96 V.

### Chapter 1

### Exercise 1.1

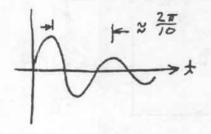

(a) For a noninverting amplifier  $A_v = +50$  and we have:  $V_o(t) = A_v V_i(t) = 50 \times 0.1 \sin(2000\pi t) = 5 \sin(2000\pi t)$

(b) For an inverting amplifier  $A_{V} = -50$  and we have:

$$v_0(t) = A_v v_i(t) = -50 \times 0.1 \sin(2000\pi t) = -5 \sin(2000\pi t)$$

### Exercise 1.2

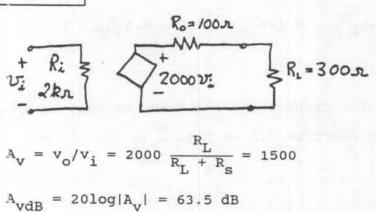

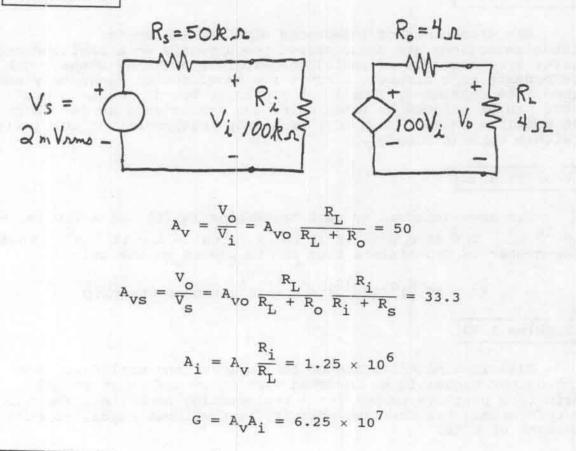

$$A_{vs} = \frac{R_{i}}{R_{s} + R_{i}} \times A_{vo} \times \frac{R_{L}}{R_{L} + R_{o}} = 300$$

$$A_{i} = A_{v} \frac{R_{i}}{R_{r}} = 10^{4}$$

$$A_{VS} = \frac{1}{R_{S} + R_{i}} \times A_{VO} \times \frac{1}{R_{L} + R_{O}} = 300$$

$A_{i} = A_{V} \frac{1}{R_{L}} = 10^{4}$   $A_{V} = \frac{V_{O}}{V_{i}} = A_{VO} \times \frac{R_{L}}{R_{L} + R_{O}} = 375$   $G = A_{V}A_{i} = 3.75 \times 10^{6}$

## Exercise 1.3

For maximum power transfer to the load, we must have  $R_L = R_O$  = 25  $\Omega$ . Then as in Exercise 1.2 we find  $A_V = 250$ ,  $A_1 = 2 \times 10^4$ , and  $G = 5 \times 10^6$ .

$$\begin{array}{c} R_{01} \\ V_{L_1} \\ R_{L_1} \end{array}$$

$$\begin{array}{c} R_{02} \\ A_{Vo_2} V_{L_2} \\ A_{Vo_2} V_{L_2} \end{array}$$

$$\begin{array}{c} R_{03} \\ A_{Vo_3} V_{L_3} \\ A_{Vo_3} V_{L_3} \end{array}$$

$$A_{vo} = A_{vo1} \frac{R_{i2}}{R_{o1} + R_{i2}} A_{vo2} \frac{R_{i3}}{R_{o2} + R_{i3}} A_{vo3} = 5357$$

$R_{i} = R_{i1} = 1000 \Omega$

$R_{o} = R_{o3} = 300 \Omega$

$$A_{vo} = A_{vo3} \frac{R_{i2}}{R_{o3} + R_{i2}} A_{vo2} \frac{R_{i1}}{R_{o2} + R_{i1}} A_{vo1} = 4348$$

$$R_{i} = R_{i3} = 3000 \Omega$$

$$R_{o} = R_{o1} = 100 \Omega$$

## Exercise 1.6

$$P_s = (1.5 \text{ A}) \times (15 \text{ V}) = 22.5 \text{ W}$$

$P_d = P_s + P_i - P_o = 20.5 \text{ W}$

$\eta = \frac{P_o}{P_s} \times 100\% = 11.1\%$

$$G = (A_V)^2 \frac{R_i}{R_r} = 1.5 \times 10^7$$

$$G_{dB} = 10logG = 71.8 dB$$

$$P_{dBW} = 10log \left[ \frac{P}{1 \text{ W}} \right] = 10log \left[ \frac{5 \times 10^{-3}}{1} \right] = -23.0 \text{ dBW}$$

$$P_{dBm} = 10log \left( \frac{P}{1 \text{ mW}} \right) = 10log \left( \frac{5 \times 10^{-3}}{10^{-3}} \right) = 10log (5) = 6.99 \text{ dBm}$$

# Exercise 1.9

$$20\log\left[\frac{V_X}{1 \text{ V}}\right] = 23 \quad \Rightarrow \quad V_X = 10^{23/20} = 14.13 \text{ V}$$

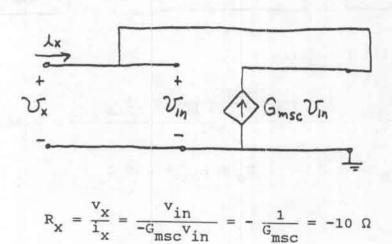

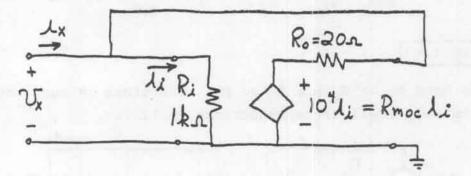

# Exercise 1.10

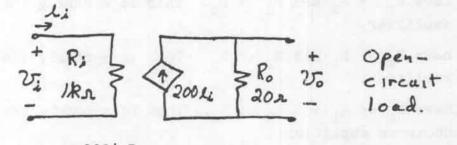

$$A_{VO} = \frac{v_O}{v_i} = \frac{200i_i R_O}{i_i R_i} = 4$$

$R_i = 1000 \Omega$   $R_O = 20 \Omega$

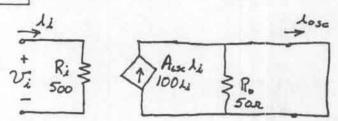

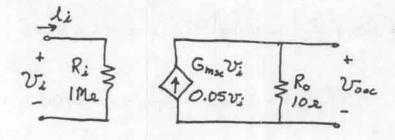

$$G_{\text{msc}} = \frac{i_{\text{osc}}}{v_i} = \frac{100i_i}{500i_i} = 0.2 \text{ s}$$

$$R_i = 500 \Omega$$

$$R_0 = 50 \Omega$$

$$R_{\text{moc}} = \frac{v_{\text{ooc}}}{i_{i}} = \frac{G_{\text{msc}}v_{i}R_{o}}{v_{i}/R_{i}} = G_{\text{msc}}R_{o}R_{i} = 500 \text{ k}\Omega$$

### Exercise 1.13

- (a) We have  $\rm R_{\rm S}$  <<  $\rm R_{\rm i}$  and  $\rm R_{\rm L}$  >>  $\rm R_{\rm o}$  . This is a nearly ideal voltage amplifier.

- (b) We have  $\rm R_{\rm S} >> \rm R_{\rm i}$  and  $\rm R_{\rm L} << \rm R_{\rm o}.$  This is a nearly ideal current amplifier.

- (c) We have  $\rm R_{s} << \rm R_{i}$  and  $\rm R_{L} << \rm R_{o}.$  This is a nearly ideal transconductance amplifier.

- (d) We have  $\rm R_{s} >> \rm R_{i}$  and  $\rm R_{L} >> \rm R_{o}.$  This is a nearly ideal transresistance amplifier.

- (e) We have  $R_s = R_i$  and  $R_L << R_o$ . This is not close to any ideal amplifier.

$$A_{cm} = v_{ocm}/v_{icm} = 0.1/1 = 0.1$$

$$A_{cmdB} = 20log|A_{cm}| = -20 dB$$

$$CMRR_{dB} = 20log \frac{|A_d|}{|A_{cm}|} = 20log \frac{50 \times 10^3}{0.1} = 114 dB$$

(a)

$$v_{id} = v_{i1} - v_{i2} = 1 \text{ V}$$

$$v_{icm} = \frac{1}{2}(v_{i1} + v_{i2}) = 0 \text{ V}$$

$$v_{o} = A_{1}v_{i1} - A_{2}v_{i2} = \frac{A_{1} + A_{2}}{2}$$

$$A_{d} = v_{o}/v_{id} = \frac{A_{1}/2 + A_{2}/2}{1} = \frac{1}{2}(A_{1} + A_{2})$$

(b)

$$v_{id} = v_{i1} - v_{i2} = 0 \text{ V}$$

$v_{icm} = \frac{1}{2}(v_{i1} + v_{i2}) = 1 \text{ V}$

$v_{o} = A_{1}v_{i1} - A_{2}v_{i2} = A_{1} - A_{2}$

$A_{cm} = v_{o}/v_{icm} = A_{1} - A_{2}$

(c)

$$CMRR = 20log \frac{|A_d|}{|A_{cm}|} = 20log \left| \frac{A_1 + A_2}{2(A_1 - A_2)} \right| = 20log \left| \frac{201}{2(100-101)} \right| = 40 \text{ dB}$$

### Problem 1.1

Some examples of electronic systems are electronic brakes, printers, cash registers, microwave ovens, CD players, airport landing systems, electronic door locks, and so forth.

### Problem 1.2

Electronic system blocks include amplifiers, filters, signal sources, wave-shaping circuits, digital logic functions, digital memories, power supplies, and converters.

### Problem 1.3

Some electronic systems process information in electronic form and some power (hopefully as little as possible) is consumed. In power electronics, the power delivered to a load is the main concern.

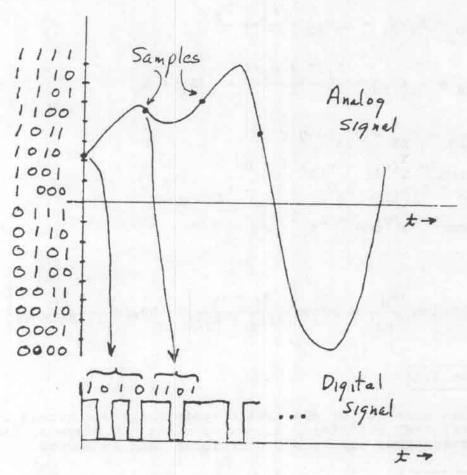

Conversion of analog signals to digital form is a two-step process. First, the signal is sampled at periodic points in time. Second, each sample is approximately represented by a codeword.

### Problem 1.5

Provided that it is not too large in amplitude, noise can be completely removed from a digital signal. Noise tends to accumulate in analog signals. Digital circuits tend to be easier than analog circuits to implement with integrated techniques. Thus extremely complex digital systems are feasible while equally complex analog systems are not. Digital systems are more adaptable than analog systems to a variety of uses.

Number of bits per second =  $16 \times 44.1 \times 10^3 = 705.6$  kbit/s (for monaural) (1.411 Mbits/s are used for stereo.)

Number of amplitude zones =  $2^{16} = 65,536$

$$\Delta = \frac{5 - (-5)}{65536} = 152.6 \ \mu V$$

### Problem 1.7

Minimum sampling rate = 2f<sub>H</sub> = 200 sample/s

$$N = \frac{10 \text{ mV}}{0.01 \text{ mV}} = 1000$$

which requires  $k = 10$  at least  $(2^{10} = 1024)$

Number of bits per second = 200 x 10 = 2 kbit/s

### Problem 1.8

See Figure 1.6 in the book.

### Problem 1.9

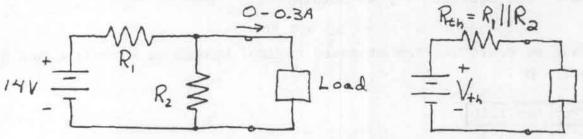

Because we are limited to resistors, the only option is a resistive voltage divider as shown below.

We denote the nominal values of the resistors as  $R_1$  and  $R_2$ . The highest load voltage (at most 6 V) occurs when  $I_L=0$ , when the resistor in parallel with the load has its highest value (which is  $1.05R_2$ ), and when the resistor in series with the source has its lowest value (which is  $0.95R_1$ ). To achieve the desired no-load voltage we need

$$14 \frac{1.05R_2}{0.95R_1 + 1.05R_2} = 6$$

Solving for R2, we have

$$R_2 = 0.6786 R_1$$

(1)

The smallest load voltage (at least 4 V) occurs with  $\rm I_L=0.3$  and resistance values of  $\rm 0.95R_2$  and  $\rm 1.05R_1$ . For these values, the Thévenin voltage is

$$V_{th} = 14 \frac{0.95 R_2}{1.05R_1 + 0.95R_2}$$

and the load voltage is

$$V_L = 4 = V_{th} - R_{th}I_L$$

$$4 = 14 \frac{0.95 R_2}{1.05 R_1 + 0.95 R_2} - 0.3 \frac{0.95(1.05) R_1 R_2}{1.05 R_1 + 0.95 R_2}$$

(2)

Using Equation (1) to substitute for  $R_2$  in Equation (2) and solving we obtain:

$$R_1 = 11.06 \Omega$$

Then from Equation (1) we obtain:

$$R_2 = 7.507 \Omega$$

Thus we could use the standard nominal values of  $\rm R_1$  = 11  $\Omega$  and  $\rm R_2$  = 7.5  $\Omega.$

### Problem 1.10

System engineers design the block diagrams of systems including specifications for each block. Circuit designers design the circuits for each block. Process engineers design the fabrication processes. Semiconductor physicists research fundamental processes used in electronic devices.

The components of integrated circuits and their interconnections are manufactured concurrently on a semiconductor wafer by a sequence of photolithographic processing steps. The components of a discrete circuit are manufactured separately and then interconnected, usually on a circuit board. Often overall cost can be reduced by integrating the system onto as few chips as possible because chip cost is nearly independent of complexity (within certain bounds).

### Problem 1.12

The area consumed by each transistor is (10  $\mu$ m)  $\times$  (10  $\mu$ m) = 10<sup>-10</sup> m<sup>2</sup>. The chip area is (2 cm)  $\times$  (2 cm) = 4  $\times$  10<sup>-4</sup> m<sup>2</sup>. Thus the number of transistors that can be placed on the chip is

$$(4 \times 10^{-4})/(10^{-10}) = 4 \times 10^{6}$$

transistors/chip

### Problem 1.13

Gain is a negative number for an inverting amplifier, and the output signal is an inverted version of the input signal. Gain is a positive number for a noninverting amplifier, and the output signal has the same polarity as the input signal at each instant of time.

### Problem 1.14

"Loading effects" refer to the fact that the input voltage of an amplifier is less than the internal source voltage because of the voltage drop across the internal source impedance. Also the amplifier output voltage is less than the open-circuit voltage gain times the input voltage because of the voltage drop across the output impedance of the amplifier.

### Problem 1.16

Using the unity-gain amplifier we have:

$$V_{s} = 100 \, \text{k.s.}$$

$$V_{s$$

With the source connected directly to the load, we have:

$$V_{S} = 100 \text{ k.}$$

$$V_{S} = 100 \text{ k.}$$

$$V_{O} = V_{S} = \frac{R_{L}}{R_{L} + R_{S}} = 2.5 \text{ mV rms}$$

$$P_{O} = V_{O}^{2}/R_{L} = 125 \text{ nW}$$

Thus the output power is much larger if the unity-gain amplifier is used.

### Problem 1.17

$$P_{in} = V_{in}^2/R_{in} = 0.333 \text{ pW}$$

$$P_{o} = V_{o}^2/R_{L} = 3.135 \text{ W}$$

$$G = P_{o}/P_{in} = 9.376 \times 10^{12}$$

### Problem 1.18

$$V_{i}$$

$R_{i}$

$A_{v_{0}}V_{i}$

$V_{i}$

$A_{v_{0}}V_{i}$

$A_{v_{0}}V_{i}$

$$A_{V} = 90 = A_{VO} \frac{R_{L}}{R_{O} + R_{L}} = 100 \frac{10^{4}}{R_{O} + 10^{4}}$$

Solving we find that  $R_0 = 1.11 \text{ k}\Omega$

With the switch open we have:

$$V_o = 50 \text{ mV} = V_s \frac{R_i}{R_i + 10^6} A_{vo} \frac{R_L}{R_L + R_o}$$

(1)

With the switch closed we have:

$$V_o = 100 \text{ mV} = V_s A_{vo} \frac{R_L}{R_L + R_o}$$

(2)

Dividing the respective sides of Equation (1) by those of Equation (2), we have:

$$\frac{50 \text{ mV}}{100 \text{ mV}} = \frac{R_{i}}{R_{i} + 10^{6}}$$

Solving we obtain  $R_i = 1 M\Omega$ .

## Problem 1.20

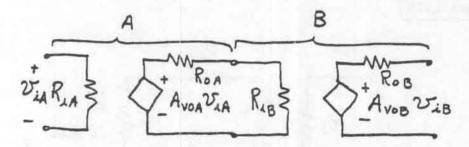

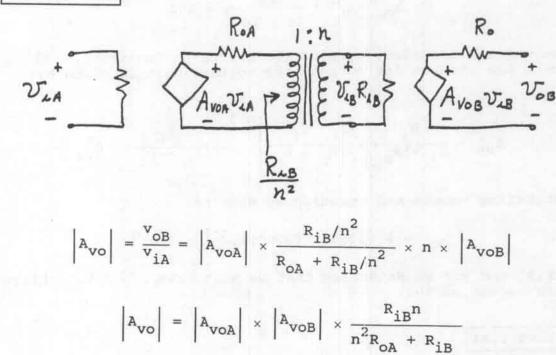

If we cascade two amplifiers A and B the equivalent circuit is:

The open-circuit voltage gain of the cascaded amplifier is:

$$A_{vo} = A_{voA}A_{voB} \frac{R_{iB}}{R_{oA} + R_{iB}}$$

### Problem 1.21

See the figure shown in the solution for Problem 1.20. When the amplifiers are cascaded in the order A-B, we have:

$$R_{i} = R_{iA} = 3 k\Omega$$

$$R_{o} = R_{oB} = 20 \Omega$$

$$A_{vo} = A_{voA}A_{voB} \frac{R_{iB}}{R_{oA} + R_{iB}} = 4.998 \times 10^{4}$$

On the other hand for the B-A cascade we have:

$$R_{i} = R_{iB} = 1 M\Omega$$

$$R_{o} = R_{oA} = 400 \Omega$$

$$A_{vo} = A_{voA}A_{voB} \frac{R_{iA}}{R_{oB} + R_{iA}} = 4.967 \times 10^{4}$$

$$\frac{d|A_{VO}|}{dn} = 0 = \left|A_{VOA}\right| \times \left|A_{VOB}\right| \times \frac{R_{iB}^2 - n^2 R_{OA} R_{iB}}{(n^2 R_{OA} + R_{iB})^2}$$

Solving for n we have:

$$n = \sqrt{\frac{R_{iB}}{R_{oA}}}$$

Problem 1.23

The internal source impedance is:

$$R_s = \frac{\text{open-circuit voltage}}{\text{short-circuit current}} = \frac{20 \times 10^{-3}}{10^{-6}} = 20 \text{ k}\Omega$$

The desired voltage gain is required to be at least:

$$A_{VS} = \frac{V_o}{V_S} = \frac{10}{20 \times 10^{-3}} = 500$$

If we cascade n stages, connect the source to the input, and connect the load to the output, the voltage gain is given by:

$$\mathbf{A_{vs}} = \frac{\mathbf{R_{i}}}{\mathbf{R_{i}} + \mathbf{R_{s}}} \times \left[\frac{\mathbf{R_{i}}}{\mathbf{R_{i}} + \mathbf{R_{o}}}\right]^{n-1} \times \frac{\mathbf{R_{L}}}{\mathbf{R_{L}} + \mathbf{R_{o}}} \times \mathbf{A_{vo}^{n}}$$

Substituting values and reducing we obtain:

$$A_{vs} = 0.02381 \times (0.9091)^{n-1} \times (10)^n$$

By trial and err we determine that we must have n=5 to achieve  $A_{_{\mbox{\scriptsize VS}}}$  in excess of 500.

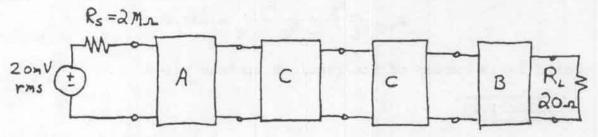

### Problem 1.24

To avoid excessive loading effects at the input, we should choose the first stage such that its input resistance is larger than the source resistance. Therefore we choose type A as the input stage. To avoid excessive loading effects at the output, we should choose the last stage such that its output impedance is much less than the load impedance. Therefore we choose type B as the output stage.

To achieve output power of 1 W we need  $P_o = 1 = V_o^2/R_L$ . Solving we determine that  $V_o = 4.472$  V rms. Thus we require an overall gain of  $A_{VS} = V_o/V_S = 4.472/(20 \times 10^{-3}) = 223.6$  as a minimum value.

To attain the required gain with the least number of stages we use intermediate stages of type C. Thus the amplifier diagram is:

The cascade has R  $_{1}$  = 10 M $\Omega$ , R  $_{0}$  = 1  $\Omega,$  and A  $_{VO}$  = 376.9. The resulting loaded gain is

$$A_{vo} \frac{R_{L}}{R_{L} + R_{o}} \frac{R_{i}}{R_{i} + R_{s}} = 299.1$$

which is in excess of the required minimum value.

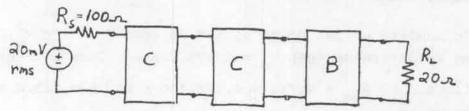

### Problem 1.25

The source impedance is lower than the input impedances of any of the stage types. Therefore we choose type C as the input stage to achieve the highest gain. To avoid excessive loading effects at the output, we should choose the last stage such that its output impedance in much less than the load impedance. Therefore we choose type B as the output stage.

To achieve output power of 1 W we need  $P_o = 1 = V_o^2/R_L$ . Solving we determine that  $V_o = 4.472$  V rms. Thus we require an overall gain of  $A_{VS} = V_o/V_S = 4.472/(20 \times 10^{-3}) = 223.6$  as a minimum value.

To attain the required gain with the least number of stages we use intermediate stages of type C. Thus the amplifier diagram is:

The cascade has R  $_{1}$  = 20 k $\Omega$ , R  $_{0}$  = 1  $\Omega,$  and A  $_{VO}$  = 452.2. The resulting loaded gain is

$$A_{VO} = \frac{R_L}{R_L + R_O} = \frac{R_i}{R_i + R_S} = 428.6$$

which is in excess of the required minimum value.

### Problem 1.26

The efficiency  $\eta$  of an amplifier is the output power divided by the supply power times 100%.

$$\eta = \frac{P_{\text{out}}}{P_{\text{supply}}} \times 100\%$$

Dissipated power is the power converted to heat.

$$P_{in} = V_{in}^2/R_{in} = (0.1)^2/10^5 = 0.1 \, \mu W$$

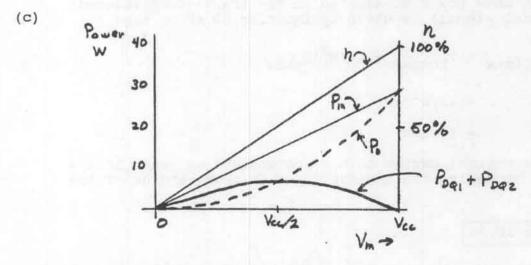

$P_{out} = V_o^2/R_L = (10)^2/8 = 12.5 \, W$

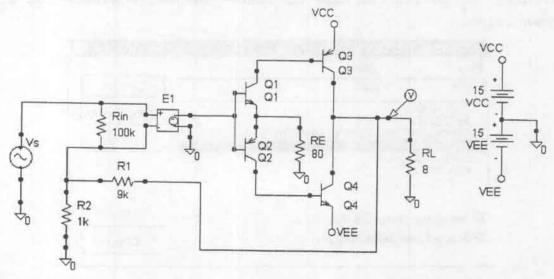

$P_{supply} = V_{cc}I_{cc} = 15 \times 2 = 30 \, W$

$P_{dissipated} = P_{supply} + P_{in} - P_o = 17.5 \, W$

$\eta = \frac{P_{out}}{P_{cumples}} \times 100\% = \frac{12.5}{30} \times 100\% = 41.67\%$

Power is delivered to the amplifier by both of the 15-V sources. Part of this power is returned to the 5-V source. The net power supplied is

$$P_{supply} = 15 \times 1 + 15 \times 2 - 5 \times 1 = 40 W$$

### Problem 1.29

$$I_{\text{lavg}} = \frac{1}{T} \int_{0}^{T} i_{1}^{2}(t) dt = \frac{1}{0.01} \int_{0}^{0.005} 2.5 \sin(200\pi t) dt = \frac{250}{200\pi} \left[ -\cos(200\pi t) \right]_{0}^{0.005} = \frac{500}{200\pi} = 0.7958 \text{ A}$$

Similarly I<sub>2avg</sub> = 0.7958 A.

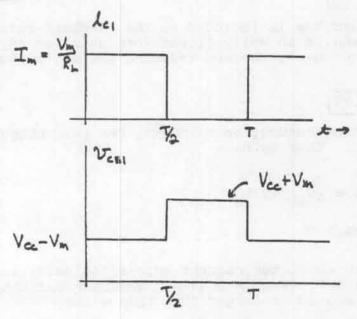

$$P_{out} = \frac{V_{o,rms}^{2}}{R_{L}} = \frac{20/\sqrt{2}}{8} = 25 \text{ W}$$

$$P_{supply} = (25 \text{ V}) \times I_{iavg} + (25 \text{ V}) \times I_{2avg} = 39.79 \text{ W}$$

$$\eta = \frac{P_{out}}{P_{supply}} \times 100\% = 62.83\%$$

### Problem 1.30

$$G_{dB} = 10\log(G)$$

$$A_{vdB} = 20log|A_v|$$

$$R_{in} = \frac{V_{in}}{I_{in}} = \frac{10 \text{ mV}}{1 \mu A} = 10 \text{ k}\Omega$$

$$A_{V} = \frac{V_{out}}{V_{in}} = \frac{5 \text{ V}}{10 \text{ mV}} = 500$$

$A_{VdB} = 20\log(A_{V}) = 53.98 \text{ dB}$

$$A_i = A_v \frac{R_{in}}{R_{I}} = 500 \frac{10 \text{ k}\Omega}{10 \Omega} = 5 \times 10^5$$

$A_{idB} = 20\log(A_i) = 113.98 \text{ dB}$

$$A_{idB} = 20log(A_i) = 113.98 dB$$

$$G = A_v A_i = 250 \times 10^6$$

$$G_{db} = 10\log(G) = 83.98 \text{ dB}$$

$$A_i = A_v \frac{R_{in}}{R_L} = 1 \times \frac{10^5}{8} = 12.5 \times 10^3$$

$A_{idB} = 20log(A_i) = 81.94 dB$

$$A_{idB} = 20log(A_i) = 81.94 dB$$

$$G = A_v A_i = 12.5 \times 10^3$$

$$G_{db} = 10\log(G) = 40.97 dB$$

# Problem 1.33

$$G_{db} = 10log(A_vA_i) = 10logA_v + 10logA_i = \frac{A_{vdB} + A_{idB}}{2} = 50 dB$$

$$A_{V} = 10^{30/20} = 31.62$$

$$A_i = 10^{70/20} = 3162$$

$$A_{i} = 3162 = A_{V} \frac{R_{i}}{R_{L}} = 31.62 \frac{100 \text{ k}\Omega}{R_{L}} \Rightarrow R_{L} = 1 \text{ k}\Omega$$

$$R_{T_i} = 1 k\Omega$$

(a) 10 dbV =

$$20\log \frac{V_a}{1 \ V}$$

$\Rightarrow$   $V_a = 10^{0.5} = 3.162 \ V$

$$V_a = 10^{0.5} = 3.162 \text{ V}$$

(b)

$$-30 \text{ dbV} = 20\log \frac{V_b}{1 \text{ V}}$$

(b)

$$-30 \text{ dbV} = 20\log \frac{V_b}{1 \text{ V}}$$

$\Rightarrow$   $V_b = 10^{-1.5} = 31.62 \text{ mV}$

(c) 10 dbmV =

$$20\log \frac{V_C}{1 \text{ mV}}$$

(c) 10 dbmV =

$$20\log \frac{V_C}{1 \text{ mV}}$$

$\Rightarrow$   $V_C = (1 \text{ mV}) \times 10^{0.5} = 3.162 \text{ mV}$

(d) 20 dBW =

$$10\log \frac{P}{1 \text{ W}}$$

$\Rightarrow$   $P = 10^2 = \frac{V_d^2}{50}$   $\Rightarrow$   $V_d = 70.71 \text{ V}$

$$P = 10^2 = \frac{V_d^2}{50}$$

$$\Rightarrow$$

$V_d = 70.71 \text{ V}$

(a) 20 dBm =

$$10\log_{\frac{1}{1}}^{\frac{P}{a}}$$

$\Rightarrow$   $P_a = (1 mW) \times 10^2 = 100 mW$

(b) -60 dBW =

$$10\log \frac{P_b}{1 \text{ W}}$$

$\Rightarrow$   $P_b = (1 \text{ W}) \times 10^{-6} = 1 \mu\text{W}$

(c) 10 dBW =

$$10\log \frac{P_C}{1 \text{ W}}$$

$\Rightarrow$   $P_C = (1 \text{ W}) \times 10^1 = 10 \text{ W}$

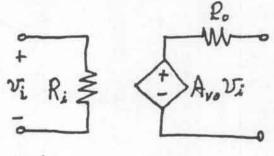

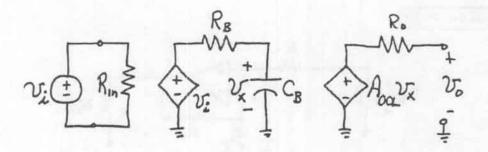

## Problem 1.36

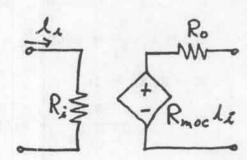

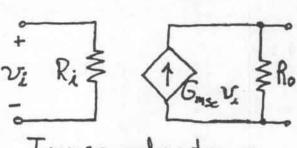

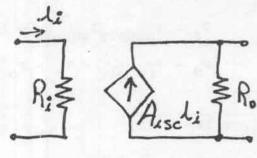

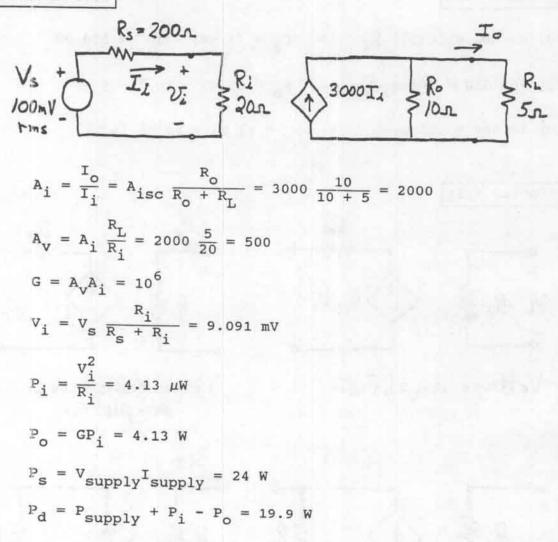

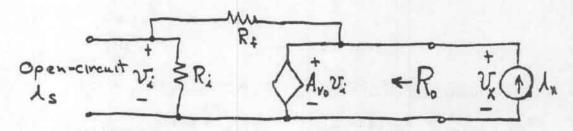

Voltage amplifier

Trans resistance amplifier

Transconductance amplifier

Current amplifier

$\mathbf{A}_{\mathrm{VO}}$  and  $\mathbf{R}_{\mathrm{moc}}$  are measured with the output open circuited.

Gmsc and Aisc are measured with the output short circuited.

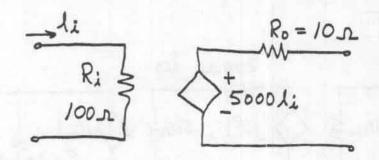

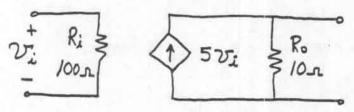

### Problem 1.38

The current amplifier model is:

(a) Voltage amplifier model:

$$A_{vo} = \frac{v_{ooc}}{v_{i}} = \frac{500i_{i}R_{o}}{R_{i}i_{i}} = 50$$

$$R_{i} = \frac{100}{100}$$

(b) Transresistance amplifier model:

$$R_{\text{moc}} = \frac{v_{\text{ooc}}}{i} = \frac{500i i^{R}_{\text{o}}}{i_{i}} = 5 \text{ k}\Omega$$

(c) Transconductance amplifier model:

$$G_{msc} = \frac{i_{osc}}{v_i} = \frac{500i_i}{R_i i_i} = 5 \text{ s}$$

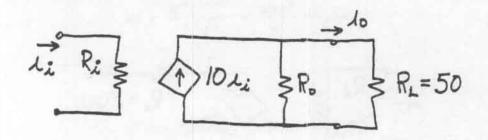

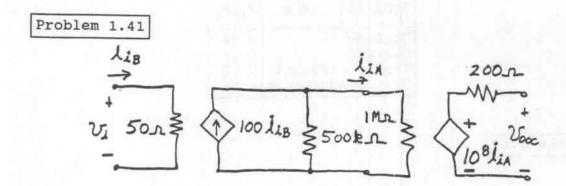

$$A_{i} = A_{isc} \frac{R_{o}}{R_{o} + R_{L}}$$

$$8 = 10 \frac{R_{o}}{R_{o} + 50} \Rightarrow R_{o} = 200 \Omega$$

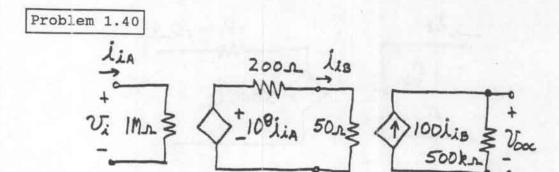

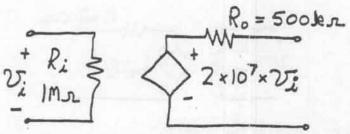

Voltage amplifier model:

$$A_{VO} = \frac{v_{OOC}}{v_{i}} = \frac{500 \times 10^{3} \times 100 \times \frac{10^{8}i_{iA}}{200 + 50}}{10^{6}i_{iA}} = 2 \times 10^{7}$$

$$R_{i} = R_{iA} = 1 M\Omega \qquad R_{o} = R_{oB} = 500 k\Omega$$

Transconductance amplifier model:

$$G_{\text{msc}} = \frac{i_{\text{osc}}}{v_{i}} = \frac{A_{\text{vo}}v_{i}/R_{o}}{v_{i}} = \frac{A_{\text{vo}}}{R_{o}} = 40 \text{ s}$$

$$v_{i} = \frac{R_{i}}{M_{A}}$$

$$V_{i} = \frac{A_{\text{vo}}v_{i}/R_{o}}{M_{A}} = \frac{A_{\text{vo}}}{R_{o}} = 40 \text{ s}$$

Voltage amplifier model:

$$A_{\text{vo}} = \frac{v_{\text{ooc}}}{v_{i}} = \frac{10^{8} \frac{500 \text{ k}\Omega}{1 \text{ M}\Omega + 500 \text{ k}\Omega} 100 \text{ i}_{\text{iB}}}{50 \text{ i}_{\text{iB}}} = 6.667 \times 10^{7}$$

$$R_{i} = R_{iB} = 50 \Omega \qquad R_{o} = R_{oA} = 200 \Omega$$

Transconductance amplifier model:

$$G_{\text{msc}} = \frac{i_{\text{osc}}}{v_{i}} = \frac{A_{\text{vo}}v_{i}/R_{o}}{v_{i}} = \frac{A_{\text{vo}}}{R_{o}} = 333.3 \times 10^{3} \text{ s}$$

$$v_{i} = \frac{R_{i}}{50.0} = \frac{A_{\text{vo}}}{R_{o}} = 333.3 \times 10^{3} \text{ s}$$

# Problem 1.42

| Amplifier type   | Ri | Ro |

|------------------|----|----|

| Voltage          | 00 | 0  |

| Current          | 0  | 00 |

| Transresistance  | 0  | 0  |

| Transconductance | 00 | 00 |

#### Problem 1.43

#### Problem 1.44

From the circuit we can write:

$$i_{i} = \frac{v_{x}}{R_{i}} \tag{1}$$

$$i_x = i_i + \frac{v_x - R_{moc}i_i}{R_o}$$

(2)

Then using Equation (1) to substitute for  $i_i$  in Equation (2) and solving, we obtain:

$$R_{x} = \frac{v_{x}}{i_{x}} = \frac{1}{\frac{1}{R_{i}} + \frac{1}{R_{o}} - \frac{R_{moc}}{R_{i}R_{o}}} = -2.23 \Omega$$

# Problem 1.45

We have R  $_{\rm i} <<$  R  $_{\rm s}$  and R  $_{\rm o} <<$  R  $_{\rm L}.$  Therefore we have a nearly ideal transresistance amplifier. Then as in Example 1.7, we have

$$R_{\text{moc}} = \frac{V_{\text{o}}}{i_{i}} = \frac{V_{\text{o}}}{V_{i}/R_{i}} = A_{\text{vo}}R_{i} = 10 \times (1 \Omega) = 10 \Omega$$

# Problem 1.46

We have  $R_i >> R_s$  and  $R_o >> R_L$ . Therefore we have a nearly ideal transconductance amplifier. Then as in Example 1.6, we have:

$$G_{\text{msc}} = \frac{i_o}{v_i} = \frac{v_o/R_o}{v_i} = \frac{A_{vo}}{R_o} = \frac{100}{10^6} = 10^{-4} \text{ s}$$

# Problem 1.47

We need R  $_{\rm i}$  >> R  $_{\rm s}$  and R  $_{\rm o}$  >> R  $_{\rm L}.$  Therefore we must have an approximately ideal transconductance amplifier.

For a 1% change in  $i_{\stackrel{}{L}}$  when  $R_{\stackrel{}{S}}$  increases from 1  $k\Omega$  to 2  $k\Omega,$  we must have

$$0.99 \times \frac{R_{i}}{R_{i} + 1000} = \frac{R_{i}}{R_{i} + 2000}$$

Solving we find that  $R_i = 98 \text{ k}\Omega$ .

For a 1% change in  $i_{\rm L}$  when  $R_{\rm L}$  increases from 100  $\Omega$  to 300  $\Omega,$  we must have

$$0.99 \times \frac{R_0}{R_0 + 100} = \frac{R_0}{R_0 + 300}$$

Solving we find that  $R_0 = 19.7 \text{ k}\Omega$ .

# Problem 1.48

We need R<sub>i</sub> < 10  $\Omega$ , R<sub>o</sub> << 10  $k\Omega$  and a transresistance gain of R<sub>moc</sub> = (1 V)/(1 mA) = 1000  $\Omega$ . Therefore we must have an approximately ideal transresistance amplifier.

To achieve approximately ±3% accuracy we will allow ±1% each for load resistance variations, amplifier gain variations, and strip chart recorder gain variations.

Allowing for a 1% increase in  $v_{_{\hbox{\scriptsize O}}}$  as  $R_{_{\hbox{\scriptsize L}}}$  increases from 10  $k\Omega$  to an open circuit, we require

$$\frac{10 \text{ k}\Omega}{R_0 + 10 \text{ k}\Omega} = 0.99$$

Solving we find that  $R_{_{\mbox{\scriptsize O}}}$  = 101  $\Omega$ , therefore we specify an amplifier with

$$R_{\text{moc}} = 1000 \Omega \pm 1\%$$

$R_{i} < 10 \Omega$

$R_{o} \leq 101 \Omega$

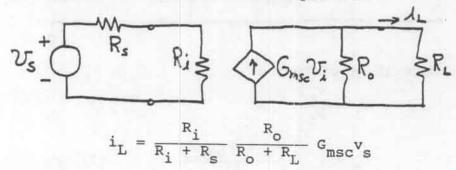

# Problem 1.49

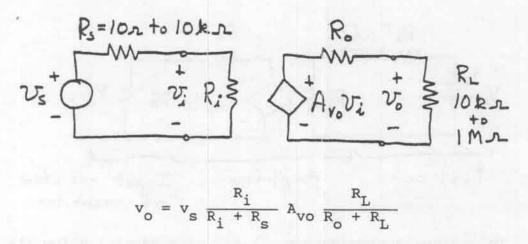

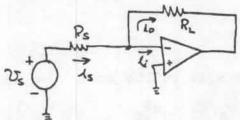

We need an amplifier with high input resistance, low output resistance, and a voltage gain of 10. Thus a nearly ideal voltage amplifier is needed. Let us allow for ±1% variations in the output voltage due to changes in source resistance, in amplifier gain, and in load resistance. The equivalent circuit for the system is:

Allowing a 1% change in  $v_{_{\mbox{\scriptsize O}}}$  when  $R_{_{\mbox{\scriptsize S}}}$  changes from 10  $\Omega$  to 10  $k\Omega,$  we require:

0.99

$$\frac{R_i}{R_i + 10} = \frac{R_i}{R_i + 10^4} \Rightarrow R_i = 9.89 \times 10^5$$

Allowing a 1% change in  $v_{_{\mbox{\scriptsize O}}}$  when  $R_{_{\mbox{\scriptsize S}}}$  changes from 1  $M\Omega$  to 10  $k\Omega,$  we require:

0.99

$$\frac{10^6}{R_0 + 10^6} = \frac{10^4}{R_0 + 10^4} \Rightarrow R_0 = 102 \Omega$$

Thus we specify an amplifier having A  $_{\rm VO}$  = 10 ± 1%, R  $_{\rm i}$  > 989 kΩ, and R  $_{\rm O}$  < 102  $\Omega.$

# Problem 1.50

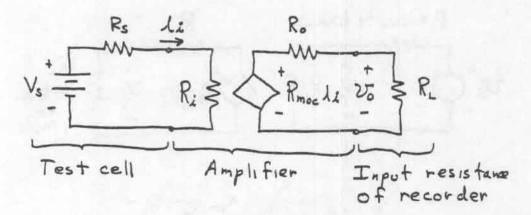

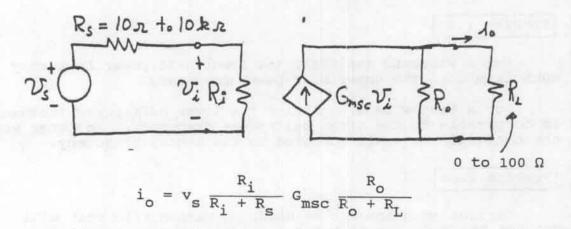

We need an amplifier with high input resistance, high output resistance, and a gain of  $G_{\rm m}=(1~{\rm mA})/(0.1~{\rm V})=10^{-2}~{\rm S}$ . The sensitivity of the recorder varies by ±1%. Therefore to achieve an overall accuracy of ±3%, let us allow ±0.667% each for variations in  $R_{\rm S}$ ,  $R_{\rm L}$ , and amplifier gain. A nearly ideal transconductance amplifier is needed. The system diagram is:

Allowing for a 0.667% change in i  $_{0}$  when R changes from 10  $\Omega$  to 10  $k\Omega,$  we require:

0.9933

$$\frac{R_{i}}{R_{i} + 10} = \frac{R_{i}}{R_{i} + 10^{4}} \Rightarrow R_{i} = 1.49 \text{ M}\Omega$$

Allowing for a 0.667% change in i  $_{\text{O}}$  when R changes from 0 to 100  $\Omega,$  we require:

$$0.9933 \frac{R_0}{R_0 + 0} = \frac{R_0}{R_0 + 100} \Rightarrow R_0 = 14.9 \text{ k}\Omega$$

Thus we need an amplifier with  $G_{\rm msc}=10^{-2}~{\rm S}\pm0.667\%,~R_{\dot{1}}>1.49~{\rm M}\Omega,$  and  $R_{\odot}>14.9~{\rm k}\Omega.$

# Problem 1.51

Any signal is the summation of sine waves of various frequencies, amplitudes, and phases. The spectrum of a signal is a plot of the amplitudes of these components versus frequency. By knowing the range of frequencies with significant amplitudes, we can specify the required frequency response for an amplifier that can amplify the signal without significant distortion.

# Problem 1.52

See Figure 1.36 in the book.

#### Problem 1.53

For a wideband amplifier the lower half-power frequency is much less than the upper half-power frequency.

For a narrow band amplifier the lower half-power frequency is comparable to the upper half-power frequency. In other words the bandwidth is small compared to the center frequency.

#### Problem 1.54

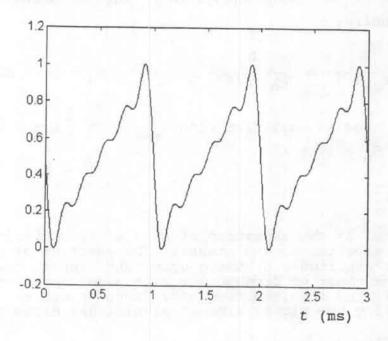

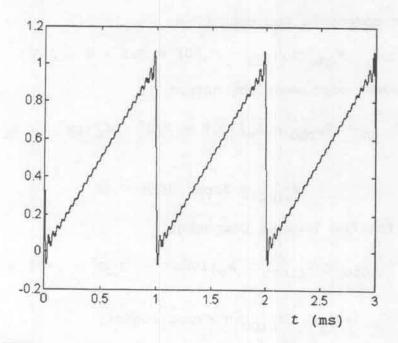

Various programs can be used. A MATLAB file that will produce the plot for 25 terms (including the constant) is:

The resulting plots are:

# Problem 1.55

The phasor for the input signal is  $V_i = 0.1/30^\circ$ . The output can be written as a cosine function:

$$v_o(t) = 10 \sin(2000\pi t + 15^\circ) = 10 \cos(2000\pi t - 75^\circ)$$

Thus the phasor for the output is  $V_0 = 10 \angle -75^\circ$ . The complex voltage gain is the output phasor divided by the input phasor.

$$A_{V} = \frac{V_{O}}{V_{i}} = \frac{10/-75^{\circ}}{0.10/30^{\circ}} = 100/-105^{\circ}$$

$$A_{vdB} = 20log|A_v| = 20log(100) = 40 dB$$

# Problem 1.56

The input signal has three components: one with a frequency of 0 (dc), one with a frequency of 100 Hz, and one with a frequency of 1000 Hz. From Figure P1.56 we have  $A_{_{\rm V}}(0)=4$ ,

$$A_{V}(100) = 4/-18^{\circ}$$

, and  $A_{V}(1000) = 2/180^{\circ} = -2$ .

For the dc component the output is:

$$v_{odc} = v_{idc} \times A_{v}(0) = 0.5 \times 4 = 2 V$$

For the 100-Hz component the output is

$$v_{ol00} = v_{il00} \times A_{v}(100) = 1/0^{\circ} \times 4/-18^{\circ} = 4/-18^{\circ}$$

Thus

$$v_{0100} = 4\cos(200\pi t - 18^{\circ})$$

Similarly for the 1000-Hz component

$$v_{o1000} = v_{i1000} \times A_{v}(1000) = 1/0^{\circ} \times (-2) = -2$$

Thus

$$v_{o100} = -2\cos(2000\pi t)$$

The output voltage is the sum of its components:

$$v_{o}(t) = 2 + 4\cos(200\pi t - 18^{\circ}) - 2\cos(2000\pi t)$$

#### Problem 1.57

$$\mathbf{v}_{o} = \mathbf{G}_{msc} \mathbf{v}_{s} \times \frac{-\mathbf{j}}{\omega \mathbf{C}}$$

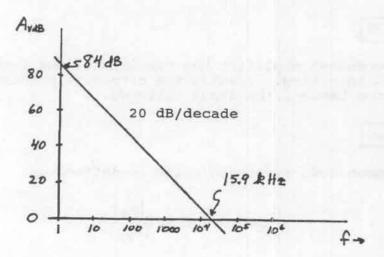

$$A_{V} = \frac{V_{O}}{V_{S}} = -j \frac{G_{mSC}}{\omega C} = -j \frac{10^{-3}}{2\pi f 10^{-8}} = -j \frac{15.9 \times 10^{3}}{f}$$

$$A_{\text{vdB}} = 20\log|A_{\text{v}}| = 20\log\left[\frac{15.9 \times 10^3}{\text{f}}\right] = 84.0 - 20\log(\text{f})$$

# Problem 1.58

We ignore the dc source because the capacitor is an open circuit at dc.

$$A_{V} = \frac{R_{i}}{R_{i} + R_{m} - j/(\omega C)} \times 100 \times \frac{R_{L}}{R_{O} + R_{L}}$$

$$A_{V} = \frac{j\omega R_{i}C}{1 + j\omega (R_{i} + R_{m})C} \times 100 \times \frac{R_{L}}{R_{o} + R_{L}}$$

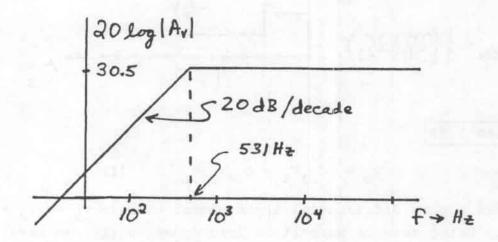

$$A_{v} = 62.83 \times 10^{-3} \times \frac{jf}{1 + j(f/531)}$$

#### Problem 1.59

A differential amplifier has two inputs, one inverting and the other noninverting. Ideally the output is proportional to the difference between the input voltages.

## Problem 1.60

The common-mode rejection ratio is defined as:

$$CMRR = 20log \frac{|A_d|}{|A_{cm}|}$$

in which  $A_d$  is the gain for the differential component and  $A_{\rm cm}$  is the gain for the common-mode signal.

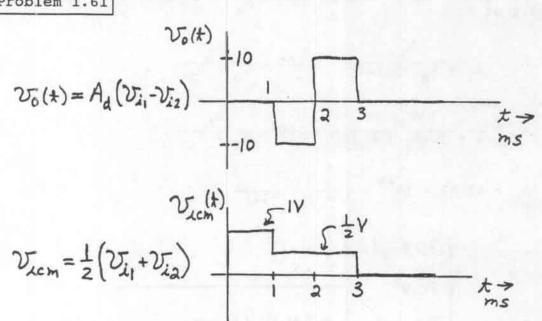

#### Problem 1.61

Problem 1.62

(a)

$$v_0 = (G_{m1}v_1 - G_{m2}v_2)R_T$$

(1)

For a pure differential input signal we have  $v_1 = -v_2 = v_{id}/2$ . Using this to substitute into Equation (1), we have

$$v_{od} = (G_{m1}v_{id}/2 + G_{m2}v_{id}/2)R_{L}$$

and the differential gain is

$$A_d = \frac{v_{od}}{v_{id}} = \frac{1}{2} (G_{m1} + G_{m2}) R_L$$

For a pure common mode input signal we have  $v_1 = v_2 = v_{icm}$ . Using this to substitute into Equation (1), we have

$$v_{ocm} = (G_{m1}v_{icm} - G_{m2}v_{icm})R_L$$

and the common-mode gain is

$$A_{cm} = \frac{v_{ocm}}{v_{icm}} = (G_{m1} - G_{m2})R_{L}$$

(b)

$$A_{d} = \frac{1}{2} (G_{m1} + G_{m2}) R_{L} = 10$$

$$A_{cm} = \frac{1}{2} (G_{m1} + G_{m2}) R_{L} = 0$$

$$CMRR = 20 \log \frac{|A_{d}|}{|A_{cm}|} = \infty$$

(c)

$$A_{d} = \frac{1}{2} (G_{m1} + G_{m2}) R_{L} = 9.95$$

$$A_{cm} = \frac{1}{2} (G_{m1} + G_{m2}) R_{L} = 0.1$$

$$CMRR = 20 \log \frac{|A_{d}|}{|A_{cm}|} = 40 \text{ dB}$$

$$v_0 = A_1 v_1 - A_2 v_2$$

(1)

For a pure differential input signal we have  $v_1 = -v_2 = v_{id}/2$ . Using this to substitute into Equation (1), we have

$$v_{od} = A_1 v_{id}/2 + A_2 v_{id}/2$$

and the differential gain is

$$A_d = \frac{v_{od}}{v_{id}} = \frac{1}{2} (A_1 + A_2)$$

For a pure common-mode input signal, we have  $v_1 = v_2 = v_{icm}$ . Using this to substitute into Equation (1), we have

and the common-mode gain is

$$A_{cm} = \frac{v_{ocm}}{v_{icm}} = A_1 - A_2$$

CMRR = 20log

$$\frac{|A_d|}{|A_{cm}|}$$

= 20 log  $\frac{|A_1 + A_2|}{2|A_1 - A_2|}$

CMRR = 20 log  $\frac{1000 + 999}{2(1000 - 999)}$  = 60 dB

## Problem 1.64

With the input terminals connected together we have a pure common-mode input signal. Thus the common-mode gain is

$$A_{CM} = \frac{v_{OCM}}{v_{icm}} = \frac{20 \text{ mV}}{10 \text{ mV}} = 2$$

CMRR = 20log

$$\frac{|A_d|}{|A_{cm}|}$$

= 20 log  $\frac{500}{2}$  = 48 dB

# Problem 1.65

The differential output is

$$V_{od} = A_d V_{id} = A_d \times (20 \text{ mV})$$

(1)

The common-mode output is

$$V_{\text{ocm}} = A_{\text{cm}} V_{\text{icm}} = A_{\text{cm}} \times (5 \text{ V})$$

(2)

The common-mode output is required to be 60 dB less than the differential output:

$$60 dB = 20\log \frac{V_{od}}{V_{OC}}$$

(3)

Using Equations (1) and (2) to substitute into Equation (3), we have

$$60 = 20 \log \frac{A_{d} \times (20 \text{ mV})}{A_{cm} \times (5 \text{ V})}$$

$$= 20\log \frac{|A_{d}|}{|A_{cm}|} + 20 \log \frac{(20 \text{ mV})}{(5 \text{ V})}$$

$$= CMRR - 48$$

$$CMRR = 108 \text{ dB}$$

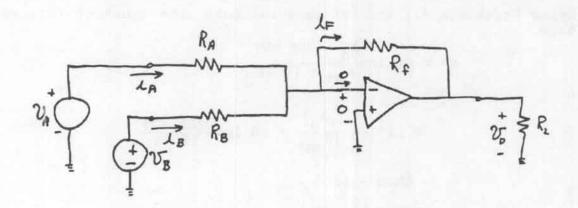

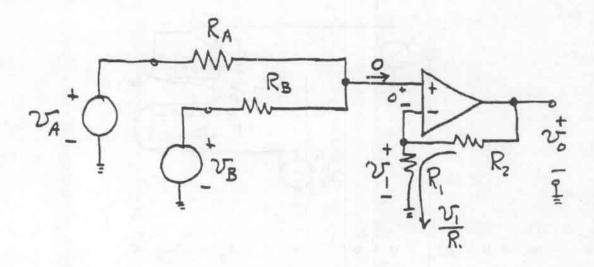

(a)

$$i_A = \frac{v_A}{R_A}$$

$i_B = \frac{v_B}{R_B}$   $i_f = i_A + i_B = \frac{v_A}{R_A} + \frac{v_B}{R_B}$

$$v_O = -R_f i_f = -\left[\frac{R_f}{R_A} v_A + \frac{R_f}{R_B} v_B\right]$$

(b) For the vA source:

$$R_{inA} = \frac{v_A}{i_A} = R_A$$

(c) for the v<sub>B</sub> source:

$$R_{inB} = \frac{v_B}{i_B} = R_B$$

(d) Because  $v_0$  is independent of  $R_{\rm L}$ , the output of the amplifier behaves as an ideal voltage source. Thus the output resistance is zero.

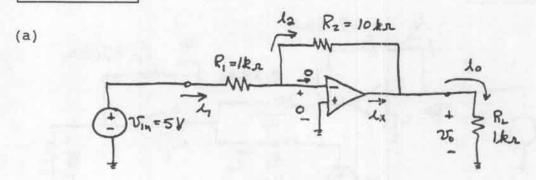

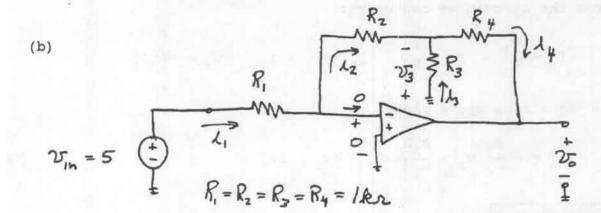

$$i_1 = \frac{v_{in}}{R_1} = 5 \text{ mA}$$

$i_2 = i_1 = 5 \text{ mA}$

$$v_0 = -R_2 i_2 = -50 \text{ V} \qquad i_0 = \frac{v_0}{R_L} = -50 \text{ mA}$$

$$i_X = i_0 - i_2 = -55 \text{ mA}$$

$$i_1 = \frac{v_{in}}{R_1} = 5 \text{ mA}$$

$i_2 = i_1 = 5 \text{ mA}$   $v_3 = R_2 i_2 = 5 \text{ V}$

$$i_3 = \frac{v_3}{R_3} = 5 \text{ mA}$$

$i_4 = i_2 + i_3 = 10 \text{ mA}$

$$v_0 = -R_4 i_4 - v_3 = -15 \text{ V}$$

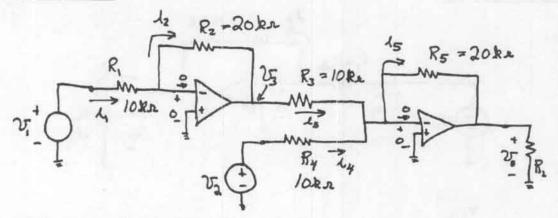

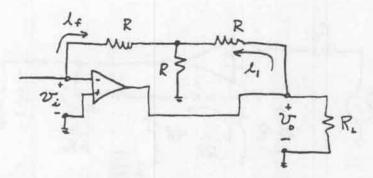

From the circuit we can write:

$$i_1 = \frac{v_1}{R_1}$$

$i_2 = i_1$   $v_3 = -R_2 i_2$

The equations above yield:  $v_3 = -\frac{R_2}{R_1} v_1 = -2v_1$

From the circuit we can write:

$$i_3 = \frac{v_3}{R_3}$$

$i_4 = \frac{v_2}{R_4}$   $i_5 = i_3 + i_4$   $v_0 = -R_5 i_5$

The equations above yield:

$$v_0 = -\frac{R_5}{R_4} v_2 + \frac{R_2 R_5}{R_1 R_3} v_1 = 4v_1 - 2v_2$$

# Exercise 2.4

$v_s = R_2 i_2 + v_{in} = v_{in}$  (because  $i_2 = 0$  by summing constraint)

$$i_1 = \frac{v_{in} - v_s}{R_1} = 0$$

$i_3 = i_1 = 0$

$v_o = -R_3 i_3 + v_s = 0 + v_{in}$

Thus  $v_o = v_{in}$  and  $A_v = v_o/v_{in} = +1$

$R_{in} = v_{in}/i_{in} = \infty$

$$i_{3} = i_{1} = \frac{v_{in}}{R_{1}} \qquad v_{o} = -R_{3}i_{3}$$

$$v_{o} = -\frac{R_{3}}{R_{1}} v_{in} \qquad A_{v} = -\frac{R_{3}}{R_{1}} = -1$$

$$R_{in} = \frac{v_{in}}{i_{in}} = \frac{v_{in}}{i_{1} + i_{2}}$$

$$= \frac{v_{in}}{v_{in}/R_{1} + v_{in}/R_{2}}$$

$$= \frac{1}{1/R_{1} + 1/R_{2}}$$

$$= \frac{R_{2}}{R_{2}}$$

$$i_2 = \frac{v_2}{R_1 + R_2}$$

$$v_s = R_2 i_2 = \frac{R_2}{R_1 + R_2} v_2$$

$$i_1 = \frac{v_1 - v_s}{R_1} = i_f$$

$$v_o = -R_2i_f + v_s$$

$$= -R_2 \frac{v_1 - v_s}{R_1} + v_s = -\frac{R_2}{R_1} v_1 + \left[1 + \frac{R_2}{R_1}\right] v_s$$

$$= - \frac{R_2}{R_1} v_1 + \frac{R_1 + R_2}{R_1} \frac{R_2}{R_1 + R_2} v_2$$

$$v_0 = \frac{R_2}{R_1} (v_2 - v_1)$$

$$V_{in} \stackrel{+}{\stackrel{-}{\longrightarrow}} \begin{array}{c} \stackrel{-}{\stackrel{-}{\longrightarrow}} \\ \stackrel{+}{\stackrel{-}{\longrightarrow}} \\ \stackrel{+}{\stackrel{+}{\longrightarrow}} \\ \stackrel{+}{\longrightarrow} \\$$

(a)

$$v_1 = v_{in}$$

$i_1 = v_{in}/R_1$   $v_2 = v_1 + R_2 i_1$

$$v_2 = v_{in} + \frac{R_2}{R_1} v_{in} = v_{in} \frac{R_1 + R_2}{R_1}$$

$$i_2 = \frac{v_2}{R_1} = v_{in} \frac{R_1 + R_2}{R_1^2}$$

$$i_3 = i_1 + i_2 = v_{in} \frac{1}{R_1} + v_{in} \frac{R_1 + R_2}{R_1^2}$$

$$i_3 = v_{in} \frac{2R_1 + R_2}{R_1^2}$$

$$v_0 = R_2 i_3 + v_2 = v_{in} \frac{R_1^2 + R_2^2 + 3R_1 R_2}{R_1^2}$$

$$A_V = \frac{v_0}{v_{in}} = 1 + 3 \frac{R_2}{R_1} + \left(\frac{R_2}{R_1}\right)^2$$

(b)

$$A_v = 131$$

(c)

$$R_{in} = v_{in}/i_{in} = v_{in}/0 = \omega$$

(d)  $v_o$  is independent of  $R_L$ , therefore  $R_o = 0$ .

For a film resistor, we have

$$\frac{L}{W} = \frac{R}{R_{D}} = \frac{6000}{300} = 20$$

If W = 10  $\mu$ m, then we must have L = 200  $\mu$ m and the area is

$$A = LW = 2000 (\mu m)^2$$

# Exercise 2.8

We have three rectangular sections with L/W=5, 4, and 5 respectively. We count the corners as 0.56 square each and the end pads as 0.65 square each. Thus we have

number of squares = 2(0.65) + 2(0.56) + 5 + 4 + 5 = 16.42

Then the resistance is the number of squares times the sheet resistance.

$$R = 16.42 \times R_{_{\square}} = 1642 \Omega$$

### Exercise 2.9

$$i_A = \frac{v_A}{R_A}$$

$i_B = \frac{v_2}{R_B}$   $i_f = i_A + i_B$

$$v_{o} = -R_{f}i_{f} = -\frac{R_{f}}{R_{A}}v_{A} - \frac{R_{f}}{R_{B}}v_{2}$$

$$v_0 = \frac{R_f R_2}{R_A R_1} v_1 - \frac{R_f}{R_B} v_2$$

Use the circuit of Figure 2.11 with  $R_2=3R_1$ . Many resistance values would work. One example is  $R_2=30~k\Omega$  and  $R_1=10~k\Omega$ . The gain of the noninverting amplifier is given by

$$A_{V} = 1 + \frac{R_{2}}{R_{1}}$$

The minimum value of  $A_{_{\mbox{\scriptsize V}}}$  occurs if  $R_{_{\mbox{\scriptsize 2}}}$  is 5% lower than its nominal value and  $R_{_{\mbox{\scriptsize 1}}}$  is 5% higher. Then the gain is

$$A_V = 1 + \frac{0.95 R_2}{1.05 R_1} = 1 + \frac{0.95}{1.05} \times 3 = 3.714$$

which is lower than the nominal value by

$$\frac{4 - 3.714}{4} \times 100\% = 7.14\%$$

Similarly the maximum value of  ${\rm A_v}$  occurs if  ${\rm R_2}$  is 5% higher than its nominal value and  ${\rm R_1}$  is 5% lower. Then the gain is

$$A_V = 1 + \frac{1.05 R_2}{0.95 R_1} = 1 + \frac{1.05}{0.95} \times 3 = 4.316$$

which is higher than the nominal value by

$$\frac{4.316 - 4}{4} \times 100\% = 7.89\%$$

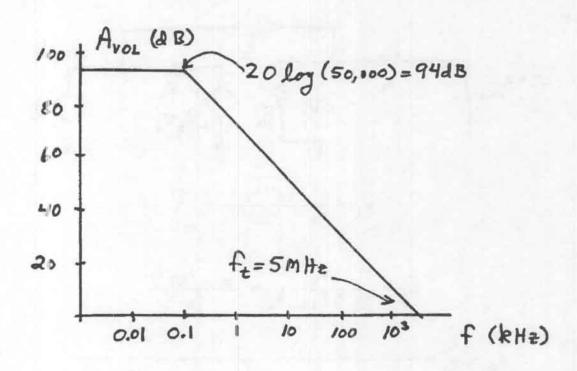

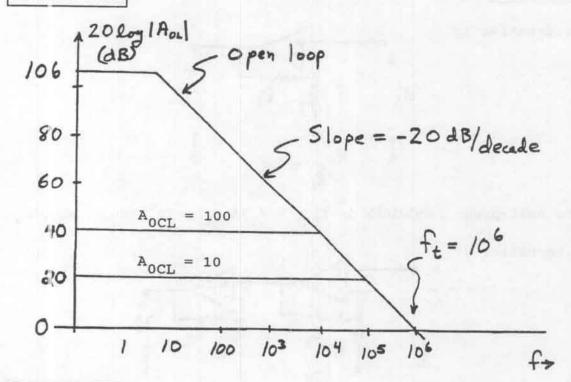

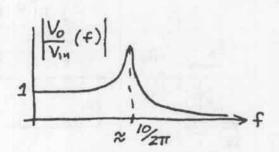

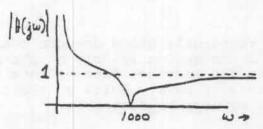

(a) From Equation (2.39) in the text we have:

$$f_{BOL} = \frac{A_{OCL}f_{BCL}}{A_{OOL}} = \frac{10 \times 200 \times 10^3}{10^6} = 2 \text{ Hz}$$

(b)

$$f_{BCL} = \frac{A_{OOL}f_{BOL}}{A_{OCL}} = \frac{10^6 \times 2}{100} = 20 \text{ kHz}$$

# Exercise 2.12

For  $A_{OOL} = 10^6$  we have

$$A_{OCL} = \frac{A_{OOL}}{1 + \beta A_{OOL}} = \frac{10^6}{1 + 0.01 \times 10^6} = 99.9900$$

For  $A_{OOL} = 0.9 \times 10^6$  we have

$$A_{OCL} = \frac{A_{OOL}}{1 + \beta A_{OOL}} = \frac{0.9 \times 10^6}{1 + 0.01 \times 0.9 \times 10^6} = 99.9889$$

The percentage change in gain is

$$\frac{99.9889 - 99.9900}{99.9900} = -1.1 \times 10^{-3}$$

# Exercise 2.13

For  $A_{OOL} = 10^6$  we have

$$A_{OCL} = \frac{A_{OOL}}{1 + \beta A_{OOL}} = \frac{10^6}{1 + 0.1 \times 10^6} = 9.99990$$

For  $A_{OOL} = 0.9 \times 10^6$  we have

$$A_{OCL} = \frac{A_{OOL}}{1 + \beta A_{OOL}} = \frac{0.9 \times 10^6}{1 + 0.1 \times 0.9 \times 10^6} = 9.99989$$

The percentage change in gain is

$$\frac{9.99989 - 9.99990}{9.99990} = -0.111 \times 10^{-3}$$

# Exercise 2.14

The circuit is shown in Figure 2.29 in the text. The op amp limits at output voltages of  $\pm 12$  V and currents of  $\pm 20$  mA. The gain of the circuit is 4. The output current of the op amp is

$$i_o = \frac{v_o}{R_1 + R_2} + \frac{v_o}{R_L}$$

(1)

- (a) For a load resistance  $R_L = 1~k\Omega$ , clipping occurs for  $v_0 = 12~V$  (or  $v_S = 3~V$ ) because the current required for a 12-V output is 15 mA which is less than the current limit of the op amp.

- (b) For a load resistance  $R_{\rm L}=200~\Omega$ , clipping occurs for  $i_{\rm O}=20~{\rm mA}$ . Using Equation (1), we find that this corresponds to an output voltage of  $v_{\rm O}=3.81~{\rm V}$  or an input voltage of 0.952 V.

## Exercise 2.15

(a)

$$f_{FP} = \frac{SR}{2\pi V_{OMax}} = \frac{5 \times 10^6}{2\pi (4)} = 199 \text{ kHz}$$

- (b) Clipping occurs when the output voltage limit occurs which is  $\pm 4$  V.

- (c) The output current is given by

$$i_0 = \frac{v_0}{R_1 + R_2} + \frac{v_0}{R_L}$$

Substituting  $i_0$  = 10 mA and the resistor values, we find  $v_{omax}$  = 0.9995 V.

(d) In this case the slew rate is the limitation.

$$V_{\text{omax}} = \frac{SR}{2\pi f} = \frac{5 \times 10^6}{2\pi 10^6} = 0.796 \text{ V}$$

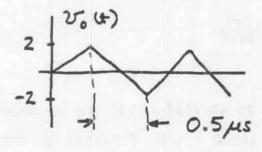

(e) The output is limited by the slew rate and is a triangular waveform. Its peak-to-peak amplitude is  $V_{p-p} = SR \times T/2$  where T = 1  $\mu s$  is the period of the waveform. Thus  $V_{peak} = V_{p-p}/2 = 1.25$  V.

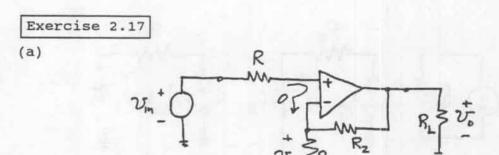

# Exercise 2.16

(a)

$$i_{in} = \frac{v_{in}}{R_1}$$

$v_o = -R_2 i_{in} = -\frac{R_2}{R_1} v_{in}$   $A_v = \frac{v_o}{v_{in}} = -\frac{R_2}{R_1}$

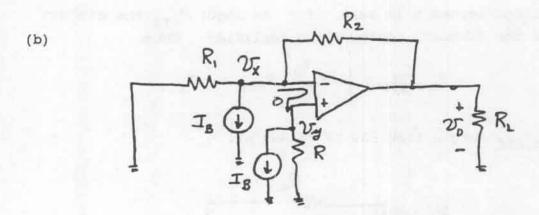

The current equation at the inverting input is:

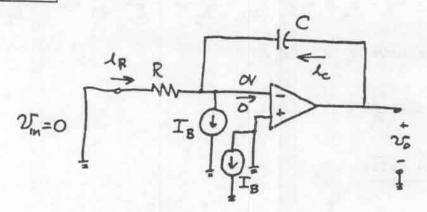

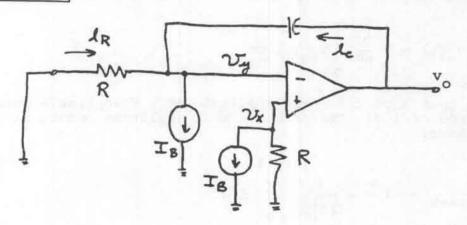

$$\frac{v_{x}}{R_{1}} + I_{B} + \frac{v_{x} - v_{o}}{R_{2}} = 0$$

(1)

Note that  $v_y = -RI_B$ . By the summing-point constraint we have  $v_x = v_y = -RI_B$ . Substituting for  $v_x$  in Equation (1) we have

$$\frac{-RI_{B}}{R_{1}} + I_{B} + \frac{-RI_{B} - v_{O}}{R_{2}} = 0$$

Then substituting R =  $\frac{R_1R_2}{R_1 + R_2}$  and solving for  $v_0$ , we find  $v_0 = 0$ .

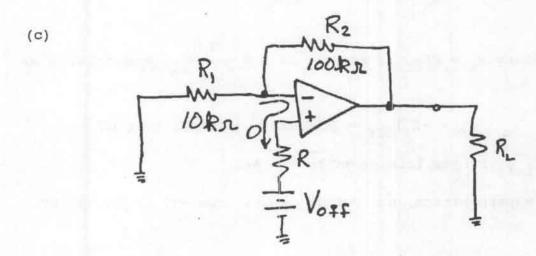

The voltage across R is zero. For the input  $V_{\mbox{off}}$  the circuit acts as the standard noninverting amplifier. Thus

$$V_{o,voff} = \left(1 + \frac{R_2}{R_1}\right) V_{off} = 11V_{off}$$

Thus Vo,off ranges from -33 mV to +33 mV.

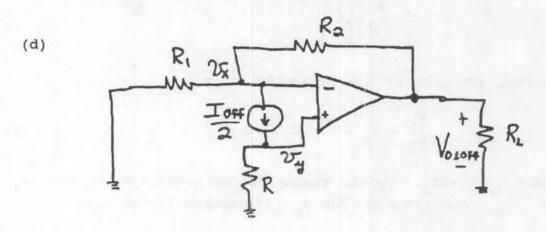

We have  $v_y = RI_{off}/2$ . Also because of the summing--point constraint we have  $v_y = v_x$ . Writing a current equation at the inverting input we have:

$$\frac{v_x}{R_1} + \frac{I_{off}}{2} + \frac{v_x - V_{o,ioff}}{R_2} = 0$$

Substituting  $v_x = RI_{off}/2$  as well as  $R = \frac{R_1R_2}{R_1 + R_2}$ , and solving we find:

$$V_{o,ioff} = -R_2I_{off} = (100 \text{ k}\Omega) \times (\pm 40 \text{ nA}) = \pm 4 \text{ mV}$$

Thus Vo, ioff ranges from -4 mV to + 4 mV.

(e) By superposition, the output ranges from -37 mV to +37 mV.

Because of the summing-point constraint, the voltage across  ${\tt R}$  is zero. Thus  ${\tt R}$  does not affect the gain.

$$v_{in} = v_1 = v_0 \frac{R_1}{R_1 + R_2} \Rightarrow A_v = \frac{v_0}{v_{in}} = 1 + \frac{R_2}{R_1}$$

Note: With  $v_0 = 0$ ,  $R_2$  appears to be in parallel with  $R_1$ .

$$v_{x} = -RI_{B} = v_{y} = -I_{B} \frac{R_{1}R_{2}}{R_{1} + R_{2}}$$

Thus we want  $R = R_1 | |R_2| = \frac{R_1 R_2}{R_1 + R_2}$

## Exercise 2.18

The equivalent circuit is:

$R_{B}$  and  $C_{B}$  act as a voltage divider and we have:

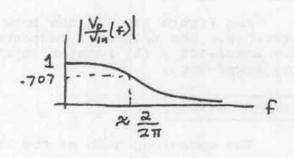

$$\mathbf{v}_{x} = \mathbf{v}_{i} \times \frac{1/(j2\pi fc_{B})}{R_{B} + 1/(j2\pi fc_{B})} = \frac{\mathbf{v}_{i}}{1 + j2\pi fR_{B}c_{B}} = \frac{\mathbf{v}_{i}}{1 + j(f/f_{BOL})}$$

With an open-circuit load the output voltage is

$$v_{o} = A_{OOL}v_{x} = \frac{A_{OOL}v_{i}}{1 + j(f/f_{BOL})}$$

Thus the transfer function for the circuit is

$$\frac{\mathbf{v_o}}{\mathbf{v_i}} = \frac{\mathbf{A_{00L}}}{1 + \mathbf{j(f/f_{BOL})}}$$

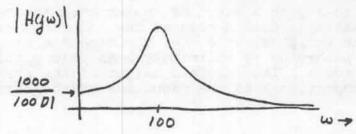

## Exercise 2.19

See the solution of Exercise 2.18 for the circuit diagram in which we must have  $R_{in}$  = 10 M $\Omega$  and  $R_{o}$  = 100  $\Omega$ . For an open-circuit dc voltage gain of 90 dB we have:

90 =

$$20\log A_{0OL}$$

$\Rightarrow$   $A_{0OL} = 10^{90/20} = 31.6 \times 10^3$

$$f_{0OL} = \frac{Gain-Bandwidth}{A_{0OL}} = \frac{15 \times 10^6}{31.6 \times 10^3} = 474.7 \text{ Hz}$$

$$c_B = \frac{1}{2\pi R_B f_{0OL}} = \frac{1}{2\pi (1000)474.7} = 0.3353 \mu F$$

The circuit file can be downloaded from the website for the text.

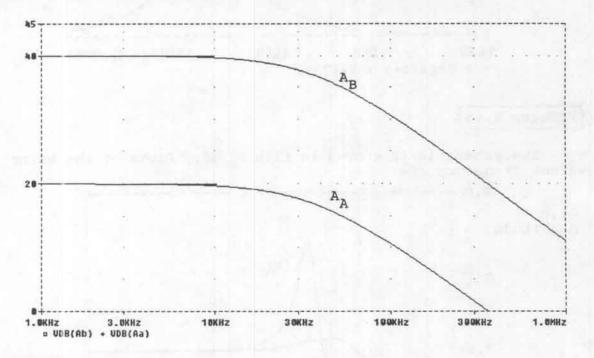

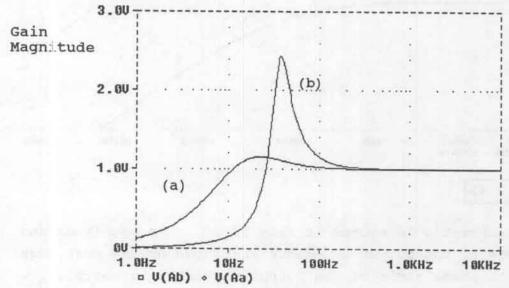

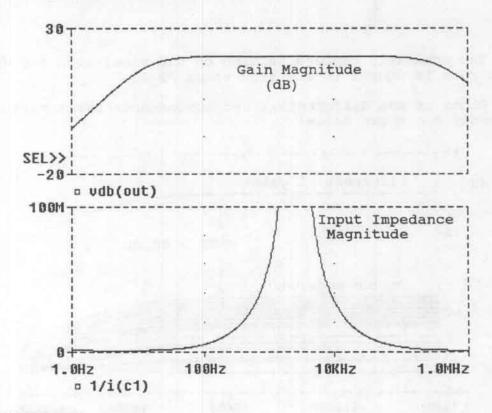

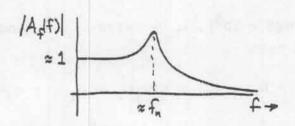

- (a) From the SPICE results we find that  $A_{\rm OCL} = 1$ ,  $f_{\rm BCL} = 4$  MHz, and gain--bandwidth = 4 MHz.

- (b)  $|A_{\rm OCL}|=1$ ,  $f_{\rm BCL}=2$  MHz, and gain--bandwidth = 2 MHz. Notice that the noninverting circuit performs best with respect to gain--bandwidth product.

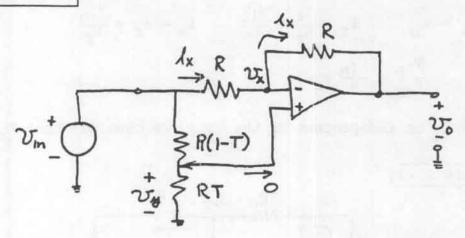

#### Exercise 2.21

$$v_y = v_{in} \frac{RT}{R(1-T) + RT} = v_{in}T$$

$v_x = v_y$  (summing-point constraint)

$$i_{x} = \frac{v_{in} - v_{x}}{R} = \frac{v_{in}}{R}$$

(1-T)

$$v_0 = -Ri_x + v_x = -v_{in}(1-T) + v_{in}T = v_{in}(2T - 1)$$

$$A_v = v_o/v_{in} = 2T -1$$

Because  $i_0$  is independent of the load, we conclude that  $R_0 = \infty$ .

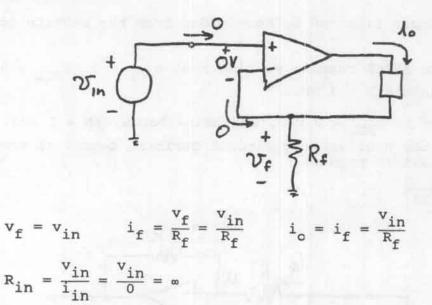

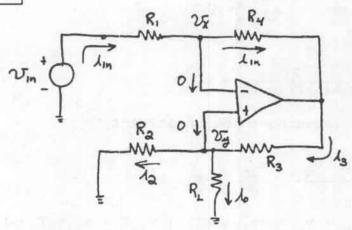

# Exercise 2.23

$$v_x = v_y = v_{in} - R_{1in}$$

$$R_4 i_{in} + R_3 i_3 = 0 \qquad \Rightarrow \qquad i_3 = -\frac{R_4}{R_3} i_{in}$$

$$i_0 = i_3 - i_2 = -\frac{R_4}{R_3} i_{in} - \frac{v_y}{R_2} = -\frac{R_4}{R_3} i_{in} - \frac{v_{in} - R_1 i_{in}}{R_2}$$

Now if we have  $R_4/R_3 = R_1/R_2$

$$i_0 = -\frac{v_{in}}{R_2}$$

# Exercise 2.24

(a)

$$v_{o}(t) = -\frac{1}{RC} \int_{0}^{t} v_{in}(t) dt = -1000 \int_{0}^{t} v_{in}(t) dt$$

$$v_{o}(t) = -1000 \int_{0}^{t} 5 dt = -5000 t \qquad 0 < t < 1 ms$$

$$= -1000 \int_{0}^{t} 5 dt - 1000 \int_{10^{-3}}^{t} (-5) dt \qquad 1 ms < t < 3 ms$$

$$= -10 + 5000 t \qquad 1 ms < t < 3 ms$$

etc.

The resulting waveform is shown in Figure 2.62 in the text.

(b)

$$v_0(t) = -\frac{1}{RC} \int_{0}^{t} v_{in}(t) dt$$

Notice that a peak-to-peak amplitude of 2 V implies a peak amplitude of 1 V. The negative peak amplitude occurs at t = 1 ms so we have:

$$V_{\text{peak}} = -1 = -\frac{1}{10^4 \text{C}} \int_{0}^{10^{-3}} 5 \text{ dt}$$

$$10^4 \text{C} = 5 \times 10^{-3}$$

$$C = 0.5 \ \mu\text{F}$$

$$i_{R} = 0/R = 0$$

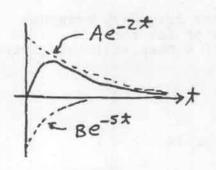

$$v_{O} = \frac{1}{C} \int_{0}^{L} i_{C} dt = \frac{1}{C} \int_{0}^{L} I_{B} dt = \frac{I_{B}}{C} t$$

(a)

$$v_0(t) = \frac{100 \times 10^{-9}}{10^{-8}} = 10t$$

(b)

$$v_0(t) = \frac{100 \times 10^{-9}}{10^{-6}} = 0.1t$$

# Exercise 2.26

$$v_y = v_x = -RI_B = -1 \text{ mV}$$

$i_R = -v_y/R = I_B$

$$i_C = I_B - i_R = 0$$

$$v_O = v_V = -1 \text{ mV}$$

$$v_{c} = \frac{1}{C} \int_{0}^{t} i_{C} dt = \frac{1}{C} \int_{0}^{t} 0 dt = 0$$

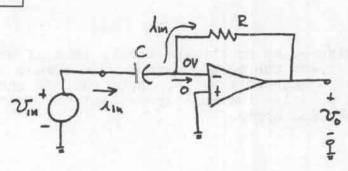

$$i_{in} = c \frac{dv_{in}}{dt}$$

$v_{o} = -Ri_{in} = -Rc \frac{dv_{in}}{dt}$

# Problem 2.1

Differential input voltage:  $v_{id} = v_1 - v_2$

Common-mode input voltage:  $v_{icm} = \frac{1}{2} (v_1 + v_2)$

# Problem 2.2

$v_{id} = v_1 - v_2 = 0.2\cos(20\pi t)$

$v_{icm} = \frac{1}{2} (v_1 + v_2) = 20\sin(120\pi t)$

# Problem 2.3

An ideal operational amplifier has the following characteristics:

- Infinite input impedance.

- Infinite open-loop gain A<sub>OL</sub> for the differential signal.

- Zero gain for the common-mode signal.

- Zero output impedance.

- Infinite bandwidth.

## Problem 2.4

Three pins are needed for each op amp: two input pins and an output pin. Thus we can have four op amps in a 14-pin package allowing two pins for power-supply connections common to all four op amps.

#### Problem 2.5

The summing-point constraint states that if negative feedback is present the op amp output will assume the value required to zero the differential input voltage and input currents. If positive feedback is present the summing-point constraint does not apply.

#### Problem 2.6

The steps in analyzing linear op-amp circuits are:

- Verify that negative feedback is present. Usually this takes the form of a resistor network connected to the output terminal and to the inverting input terminal.

- Assume that the differential input voltage and the input current of the op amp are forced to zero. (This is the summingpoint constraint.)

- Apply standard circuit analysis principles, such as Kirchhoff's laws and Ohm's law, to solve for the quantities of interest.

## Problem 2.7

In a shower we use negative feedback to adjust water temperature. If it is too hot we increase the cold-water flow or reduce the hot-water flow. We adjust until the difference between actual temperature and desired temperature is driven to zero.

In driving an automobile on a two-lane highway in the United States we adjust the position of our vehicle to remain centered in the right-hand lane. If we are too close to the edge of the highway we steer toward the center, if we are too close to the center we steer to the right.

#### Problem 2.8

Positive feedback is a problem when we have a fire in a building. When a fire first starts heat is created which vaporizes additional fuel increasing the size of the fire. Usually positive feedback is self limiting. In the case of a building fire, the fire dies out when the building is totally consumed.

When our children behave well we give them positive feedback encouraging them to continue their good behavior.

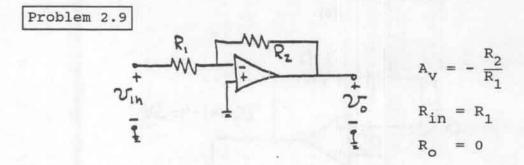

Notice that  $A_V = -R_2/R_1 = -10$ . For  $v_0 = 12$  V, we have  $v_{\rm in} = v_0/A_V = 12/(-10) = -1.2$  V and  $v_{\rm x} = v_0/(-A_{\rm OL}) = 12/(-10^4) = -1.2$  mV. Thus  $v_{\rm x}$  is 1000 times less than  $v_{\rm in}$ , and  $v_{\rm x}$  can be assumed to be zero with sufficient accuracy for most applications. Thus we are justified in using the summing-point constraint for this circuit.

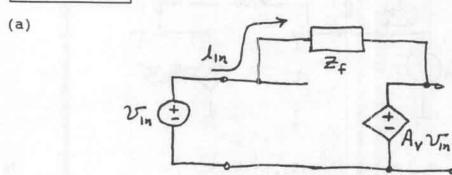

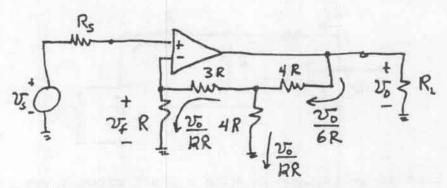

## Problem 2.12

$$I_{in} = \frac{v_{in} - A_v v_{in}}{Z_f}$$

$\Rightarrow$   $Z_{in} = \frac{v_{in}}{I_{in}} = \frac{Z_f}{1 - A_v}$

(b)

$$Z_{in} = \frac{Z_f}{1 - A_v} = \frac{10^4}{1 - (-10^5)} \approx 0.10 \Omega$$

The input impedance is very low. If an impedance were placed in series with  $v_{\rm in}$  (as in an inverter) the input voltage to the op amp would be driven to zero as the op amp open-loop gain approaches infinity (just as we assume when we use the summing-point constraint).

(c)

$$Z_{in} = \frac{Z_f}{1 - A_V} = \frac{10^4}{1 - 2} = -10 \text{ k}\Omega$$

The input impedance is a negative resistance. This is a positive feedback situation.

(d)

$$z_{in} = \frac{z_{f}}{1 - A_{V}} = \frac{\frac{1}{j\omega C}}{1 - (-100)} = \frac{1}{j\omega(99C)}$$

The input impedance is that of a 99-pF capacitance. This situation often occurs in amplifiers because of device capacitances and is a significant problem when extended high-frequency response is needed.

## Problem 2.13

The equivalent circuit is:

$$V_{in} \stackrel{f}{=} V_{x}$$

$$V_{in} \stackrel{f}{=} V_{x}$$

$$\mathbf{v}_{in} = (\mathbf{R}_1 + \mathbf{R}_2)\mathbf{I}_{in} - \mathbf{A}_{oL}\mathbf{v}_{x} \tag{1}$$

$$\mathbf{v}_{\mathbf{x}} = \mathbf{v}_{\mathbf{in}} - \mathbf{R}_{\mathbf{1}} \mathbf{I}_{\mathbf{in}} \tag{2}$$

Using Equation (2) to substitute for  $\mathbf{V}_{\mathbf{X}}$  in Equation (1) and solving for the input impedance, we find

$$z_{in} = \frac{v_{in}}{I_{in}} = R_1 + \frac{R_2}{1 + A_{OL}}$$

Evaluating for  $R_1 = 1 k\Omega$ ,  $R_2 = 10 k\Omega$ , and  $A_{OL} = 10^4$ , we find

$$Z_{in} = 1001 \Omega$$

The input impedance assuming infinite AoL is

$$z_{in} = R_1 = 1000 \Omega$$

The percentage difference between the two answers is 0.1%

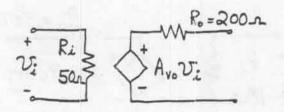

### Problem 2.14

Starting from the input and working toward the output we can determine the voltages and currents shown below:

Eventually we determine that  $v_0 = 8v_{in}$  so we have a closed loop voltage gain of 8.

The circuit diagram for the inverting amplifier is shown in Figure 2.5 in the text. The gain of an inverting amplifier is  $A_V = -R_2/R_1$ . The largest gain magnitude occurs if  $R_2$  is 1% high and  $R_1$  is 1% low in which case we have

$$A_{V} = -\frac{1.01R_{2nom}}{0.99R_{1nom}} = 1.020 A_{vnom}$$

in which  $\rm R_{1nom}$  is the nominal value of  $\rm R_1,\ R_{2nom}$  is the nominal value of  $\rm R_2$  and  $\rm A_{vnom}$  is the nominal gain.

Similarly, for the opposite extreme we obtain  $A_{\rm v} = 0.980 A_{\rm vnom}$ . Thus the tolerance of the closed-loop gain is ±2%.

### Problem 2.16

The equivalent circuit is:

$$\frac{v_{x} - v_{in}}{R_{1}} + \frac{v_{x} - v_{o}}{R_{2}} = 0 {1}$$

$$v_{o} = -A_{OL}v_{X}$$

(2)

Solving Equation (2) for  $v_{\chi}$ , substituting into Equation (1), and applying algebra yields

$$A_{V} = \frac{-R_{2}A_{OL}}{R_{2} + R_{1} + A_{OL}R_{1}}$$

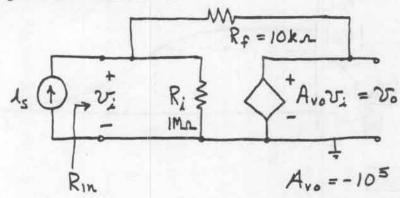

For  $R_1$  = 1 k $\Omega$ ,  $R_2$  = 10 k $\Omega$  and  $A_{OL}$  = 10<sup>4</sup> we obtain  $A_V$  -9.989. For  $A_{OL}$  = 10<sup>5</sup>, we obtain  $A_V$  = -9.998. As  $A_{OL}$  approaches infinity,  $A_V$  approaches - $R_2/R_1$  = 10.

### Problem 2.17

Kirchhoff's current law may not seem to be satisfied for the opamp terminals if we do not consider the power-supply terminals. However if we considered the power-supply currents, the equation

$$I_{+} + 11 mA = I_{-}$$

would be satisfied. Not enough information is given in the problem to determine the power-supply currents.

### Problem 2.18

$$v_{o1} = v_3$$

$i_{in} = \frac{v_{in}}{R}$   $i_4 = i_3 = v_{o1}/R$

$$A_V = 1 + R_2/R_1$$

$R_{in} = \omega$   $R_0 = 0$

# Problem 2.20

# Problem 2.21

The voltage follower has a very large input impedance (ideally infinite) and a very low output impedance (ideally 0). If the source impedance is much larger than the load impedance and the load is connected directly to the source, the load voltage is much less than the open-circuit source voltage. By using the voltage follower, the load voltage can be nearly equal to the open-circuit source voltage.

$$\frac{v_1 - v_A}{R_A} + \frac{v_1 - v_B}{R_B} = 0 \qquad \Rightarrow \qquad v_1 = \frac{v_A R_B + v_B R_A}{R_A + R_B}$$

$$v_0 = v_1 + R_2 \frac{v_1}{R_1} = \frac{R_1 + R_2}{R_1} v_1$$

$$v_o = \frac{R_1 + R_2}{R_1} \times \frac{v_A R_B + v_B R_A}{R_A + R_B}$$

$$v_o = A_A v_A + A_B v_B$$

where

$$A_A = \frac{R_1 + R_2}{R_1} \times \frac{R_B}{R_A + R_B}$$

and

$$A_B = \frac{R_1 + R_2}{R_1} \times \frac{R_A}{R_A + R_B}$$

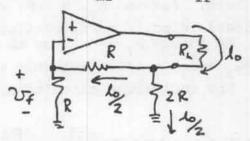

$$v_1 = 0 + Ri_0 + 0 + v_2 \Rightarrow i_0 = \frac{v_1 - v_2}{R}$$

Because  $i_0$  is independent of the load we conclude that the output impedance is infinite.

Loop 1:  $v_{in} = Ri_{in} + 0 + Ri_{in}$

Loop 2:  $Ri_{in} + R_{fi_0} + Ri_{in} = 0$

Solving:  $i_o = -v_{in}/R_f$

Because  $i_0$  is independent of the load, we conclude that the output impedance is infinite.

(a)

$$A_{V} = \frac{V_{O}}{V_{in}} = -\frac{R_{2}}{R_{1}}$$

$P_{in} = \frac{V_{S}^{2}}{R_{1}}$   $P_{O} = \frac{V_{O}^{2}}{R_{L}} = \frac{R_{2}^{2}V_{S}^{2}}{R_{1}^{2}R_{L}}$   $G = \frac{P_{O}}{P_{in}} = -\frac{R_{2}^{2}}{R_{1}^{2}R_{L}}$

(b)  $P_{in} = 0$  because  $I_{in} = 0$ . Therefore  $G = P_{o}/P_{in} = \infty$ . Thus the noninverting amplifier has the higher power gain.

## Problem 2.25

(a)

$$v_o = -R_{fin}$$

- (b) Because  $\mathbf{v}_{o}$  is independent of  $\mathbf{R}_{L}$ , the output behaves as an ideal voltage source and the output resistance is zero.

- (c) The input voltage is zero because of the summing-point constraint. Therefore  $R_{in} = 0$ .

- (d) This is an ideal transresistance amplifier.

## Problem 2.26

Because  $A_V = -R_2/R_1$ , we select the nominal resistances such that  $R_{2\text{nom}} = 2R_{1\text{nom}}$ . Given 5%-tolerances we have

$$R_{1min} = 0.95R_{1nom}$$

$R_{1max} = 1.05R_{1nom}$

$R_{2min} = 0.95R_{2nom}$   $R_{2max} = 1.05R_{2nom}$

Then the minimum gain magnitude is

$$|A_{V}|_{\min} = \frac{R_{2\min}}{R_{1\max}} = \frac{0.95R_{2nom}}{1.05R_{1nom}} = 1.81$$

Similarly

$$|A_V|_{max} = \frac{R_{2max}}{R_{1min}} = \frac{1.05R_{2nom}}{0.95R_{1nom}} = 2.21$$

The tolerances of the gain magnitude are -9.5% and +10.5%.

## Problem 2.27

Because  $A_v = 1 + R_2/R_1$ , we select the nominal resistances such that  $R_{2\text{nom}} = R_{1\text{nom}}$ . Given 5%-tolerances we have

$$R_{1min} = 0.95R_{1nom}$$

$R_{1max} = 1.05R_{1nom}$

$R_{2min} = 0.95R_{2nom}$   $R_{2max} = 1.05R_{2nom}$

Then the maximum gain magnitude is

$$|A_{V}|_{\min} = 1 + \frac{R_{2\min}}{R_{1\max}} = 1 + \frac{0.95R_{2nom}}{1.05R_{1nom}} = 1.905$$

Similarly

$$|A_{V}|_{\text{max}} = 1 + \frac{R_{2\text{max}}}{R_{1\text{min}}} = 1 + \frac{1.05R_{2\text{nom}}}{0.95R_{1\text{nom}}} = 2.105$$

The tolerances of the gain magnitude are -4.75% and +5.25%.

(a) This circuit has negative feedback. For an ideal op amp we have  $v_0(t) = v_{in}(t)$ .

(b) This circuit has positive feedback. The summing-point constraint does not apply. Instead either  $v_0 = +5$  V or  $v_0 = -5$  V.

Notice that  $v = v_0 - v_{in}$ . If v > 0,  $v_0 = +5$  V. On the other hand if v < 0,  $v_0 = -5$  V.

(a) This circuit has negative feedback. For an ideal op amp we have  $v_0(t) = -v_{in}(t)$ .

This circuit has positive feedback and the summing-point constraint does not apply. Writing a current equation at the noninverting input of the op amp yields

$$\frac{v - v_{in}}{R} + \frac{v - v_{o}}{R} = 0 \quad \Rightarrow \quad v = \frac{v_{o} + v_{in}}{2}$$

If v > 0 then  $v_0 = +5$  V. On the other hand if v < 0,  $v_0 = -5$ .

The sheet resistances of the various layers are commonly optimized for purposes, such as the base regions of BJTs, other than fabricating resistors. Adding more steps to the process to create layers optimized for resistors would reduce yield and increase cost.

### Problem 2.31

Very small resistances imply large currents and high power dissipation. Very large resistances are subject to stray coupling of undesired signals. Furthermore, resistances of either extreme are likely to require excessive chip area because  $R = R_{\square} L/W$  and we need to have  $L \cong W$  for minimum area.

### Problem 2.32

Doubling the thickness of the layer creates a second identical resistor above or below the original resistor. The resistors are electrically in parallel. Thus the resistance is reduced by a factor of 2. If we double the thickness of a 200- $\Omega$  layer, the sheet resistance R is reduced to 100  $\Omega$ .

## Problem 2.33

We should choose the width of the conductors to be W = 10  $\mu m$  to minimize the area consumed. For a resistor composed of a single straight conductor, we would have L = WR/R = 10(10^4/200) = 500  $\mu m$ . Including the guard strips the area consumed is (20  $\mu m$ )  $\times$  L = 10  $^4$   $\mu m^2$ .

Because we want the resistor to occupy an approximately square area, we need W $_R=L_R\cong\sqrt{A}=100~\mu m$ . Thus, we need W $_R/(20~\mu m)=5$  or 6 conductors. We propose the layout composed of 5 conductors:

For this layout, the resistance is the sum of:

Thus we need 10  $^4$   $\Omega$  = 100L $_R$  - 844 which yields L $_R$  = 108.4  $\mu m$

Problem 2.34

Here is one solution:

$$R_{in} = R_1 = 10 \text{ k}\Omega$$

$R_2 = 20 \text{ k}\Omega$   $R_3 = 180 \text{ k}\Omega$

A simple answer is the standard inverter shown in Figure 2.5 in the text with  $R_1$  = 1  $k\Omega$  and  $R_2$  = 100  $k\Omega$  for a total resistance of 101  $k\Omega$ .

A better answer is the circuit shown in Figure 2.6 in the text with  $R_1=R_3=1$  k $\Omega$  and  $R_2=R_4=9.05$  k $\Omega$  for a total resistance of 20.1 k $\Omega$ . (See the analysis of this circuit in Example 2.1 in the text.)

Very likely still better answers exist.

### Problem 2.36

A good answer is to cascade two noninverting amplifiers like the one shown in Figure 2.11 in the text. Each amplifier should have  $R_1$  = 1  $k\Omega$  and  $R_2$  = 9  $k\Omega$ . The total resistance is 20  $k\Omega$  and two op amps are used. The total area consumed is that of 4 op amps. (We assume that area is proportional to resistance.)

Another good answer is the circuit of Figure 2.15 analyzed in Exercise 2.6 with R $_1$  = 1 k $\Omega$  and R $_2$  = 8.56 k $\Omega$  for a total area equal to nearly 3 op amps.

## Problem 2.37

Here are two answers:

Two possibilities are to place unity-gain voltage followers between the sources and the inputs of the circuits designed for Problem 2.37. A better answer that uses fewer op amps is:

Problem 2.39

Here is one answer:

Op amp imperfections in the linear range of operation include:

- finite input impedance

- m nonzero output impedance

- finite open-loop gain

- finite bandwidth

- nonzero common-mode gain

### Problem 2.41

For the noninverting amplifier with a given op amp, the product of dc gain and closed-loop bandwidth is constant as the dc gain is changed.

### Problem 2.42

(a) Refer to Figure P2.42 in the text.

$$v_{s} = R_{in}i_{s} + R_{o}i_{s} + A_{OL}(R_{in}i_{s})$$

$$v_{o} = R_{o}i_{s} + A_{OL}(R_{in}i_{s})$$

$$A_{vs} = \frac{v_{o}}{v_{s}} = \frac{R_{o} + A_{OL}R_{in}}{R_{in} + R_{o} + A_{OL}R_{in}}$$

$$A_{vs} = \frac{25 + 10^{5} \times 10^{6}}{10^{6} + 25 + 10^{5} \times 10^{6}} = 0.99999$$

The gain would be 1.00000 for an ideal op amp.

(b)

$$Z_{in} = \frac{v_s}{i_s} = R_{in} + R_o + A_{OL}R_{in} = 10^{11} \Omega$$

In comparison, we would have  $Z_{in} = \infty$  for an ideal op amp.

$$\begin{array}{c} \mathcal{V}_{i} = 0 \\ \mathcal{V}_{i} = 0 \\ \end{array} \qquad \begin{array}{c} \mathcal{V}_{i} \\ \end{array} \qquad \begin{array}{c} \mathcal{R}_{i} \\ \end{array} \qquad \begin{array}{c}$$

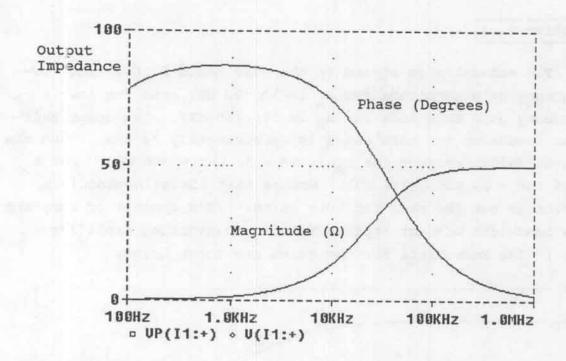

$$v_i = -v_x$$

$i_x = \frac{v_x}{R_{in}} + \frac{v_x - A_{OL}v_i}{R_O}$   $Z_O = \frac{v_x}{i_x} = \frac{1}{\frac{1}{R_{in}} + \frac{1 + A_{OL}}{R_O}}$

Evaluating we find  $Z_0 = 2.5 \times 10^{-4} \Omega$  compared to  $Z_0 = 0$  for an ideal op amp.

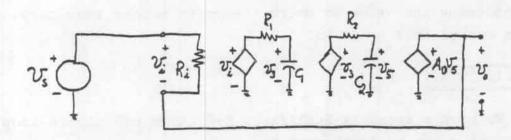

## Problem 2.43

(a) Refer to Figure P2.43 in the text. Writing current equations at the input terminal of the op amp and at the output terminal we have:

$$\frac{v_s + v_i}{R_1} + \frac{v_o + v_i}{R_2} + \frac{v_i}{R_{in}} = 0$$

(1)

$$\frac{v_{o} + v_{i}}{R_{2}} + \frac{v_{o} - A_{OL}v_{i}}{R_{O}} = 0$$

(2)

Now we solve Equation (1) for  $v_i$ , substitute into Equation (2), and use algebra to obtain:

$$A_{vs} = \frac{v_{o}}{v_{s}} = \frac{-R_{2}}{R_{1} \left[ 1 + \left[ \frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{in}} \right] \frac{R_{o}R_{2} + R_{2}^{2}}{A_{oL}R_{2} - R_{o}} \right]}$$

Evaluating we find  $A_{VS} = -9.9989$  compared to  $A_{VS} = -10$  for an ideal op amp.

(b) From the circuit we can write:

$$v_s = R_1 i_s - v_i \tag{3}$$

$$v_i + (R_1 + R_0) \left[ \frac{v_i}{R_{in}} + i_s \right] + A_{OL} v_i = 0$$

(4)

Now we solve Equation (3) for  $v_i$ , substitute into Equation (4), and use algebra to obtain:

$$z_{in} = \frac{v_s}{i_s} = R_1 + \frac{R_2 + R_o}{1 + A_{oL} + \frac{R_2 + R_o}{R_{in}}}$$

Evaluating we find Z  $_{\mbox{in}}$  = 1.0001  $k\Omega$  compared to Z  $_{\mbox{in}}$  = 1.0000  $k\Omega$  for an ideal op amp.

$$v_{i} = \frac{R_{in}^{||R_{1}}}{R_{2} + R_{in}^{||R_{1}}} v_{x}$$

$$v_{i} = \frac{V_{x}}{R_{2} + R_{in}^{||R_{1}}} v_{x}$$

$$i_{x} = \frac{v_{x}}{R_{2} + R_{in}^{||R_{1}}} + \frac{v_{x} - A_{0L}v_{i}}{R_{0}}$$